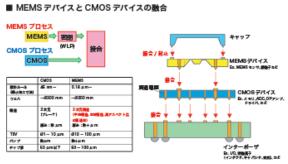

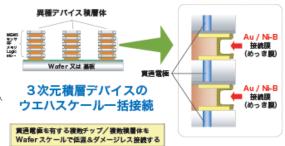

## (2)-2. MEMS/半導体の一体形成技術の開発 - MEMS-半導体横方向配線技術 - (産業技術総合研究所)

#### I. 研究の概要

#### 特徴

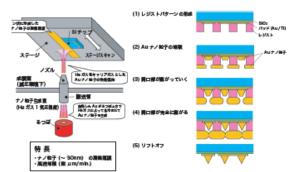

本技術は、工業用インクジェット技術において、レーザー 照射によりインク液滴の乾燥を促進することによって、基板に着弾後のインクの濡れ拡がりを抑制する。これにより、従来困難とされていた描画線幅の微細化と線厚みの厚膜化の両立が可能となった。現状で、重ね塗りすることなくアスペクト比が 1 以上、線幅 10 μm 以下の微細導体パターンを10mm/sec の速さで描画できることが確認され、従来インクジェット技術の微細配線領域で課題となっていた配線長さ当たりの抵抗値を、約 10 倍以上低減することができるようになった。

#### 技術内容・特性

#### 用途・目的

製品仕様の多様化や製品サイクルの短期化に伴い、電子デバイス製造では小型、低コスト化だけでなく、多品種・少量生産に対応できるオンデマンドな設計・製造技術が求められている。本レーザー援用インクジェット技術は、基板の材質や表面状態によらず微細配線の描画が可能であるため、Si チップー樹脂—Si チップ上にも直接描画することも可能である。このような特徴を通し、MEMS- 半導体の高集積化実装や FDP などの大面積デバイスの実装技術として展開可能と考えられる。今後は、本技術の特徴を生かし、さまざまな材料への適用、用途展開を進め、実装コストの大幅な低減や設計・仕様変更あるいは、カスタムメイドに対応できる実装技術に発展させる。

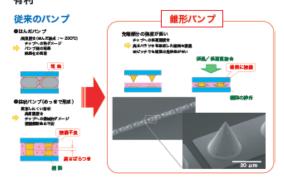

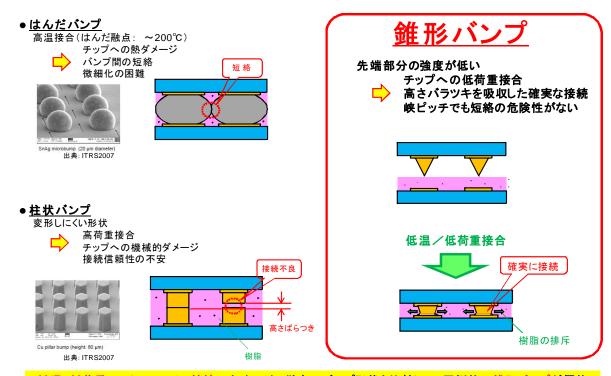

#### 特 徴

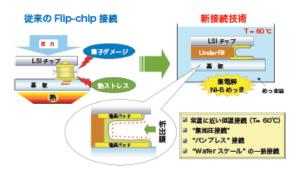

低ストレスで狭ピッチの接続には、錐形パンプが圧倒的に 有利

#### 技術内容・特性

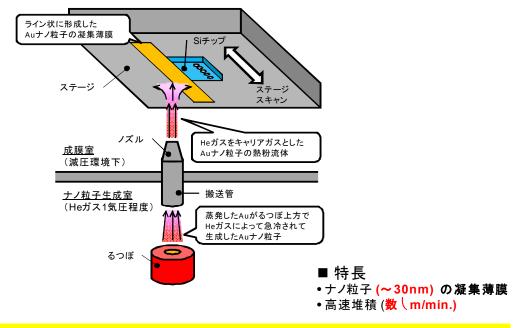

ガスデポジション法により自己形成的に錐形パンプを形成 ■ ガステポジション (GD) 法 ■ プロセスフロー (形成メカニズム)

#### 用途・目的

バンプ接合において、機械的強度の低い3次元構造をもつ MEMS デバイスには、低温・低荷重の接続技術が必要不可欠

#### 特徴

カと熱を用いた従来の"物理的実装"から、低温でダメージレスの "化学的実装" へ

#### 技術内容・特性

無電解めっきの"ブリッジ不良"を積極的に利用して、10μm 以下の超微細ピッチ接続を実現

#### 用途・目的

超微細電極を有する各種デバイスの"常温ダメージレス接続" "ウエハースケール3次元積層実装"

#### Ⅱ. 成果の詳細

#### 1. はじめに

本研究開発では、原材料溶液にレーザーによるエネルギー援用を行い、微細ノズル通過時は、 液相状態とし、ノズル吐出後、一度、活性の高い固体状態の超微粒子や高粘度ゲルを形成してか ら、基板上に高速着弾させる。また、溶媒蒸発エネルギー援用条件の最適化を図るために、原材 料となるナノインク、ナノペーストを構成する超微粒子材料、搬送溶媒(液相)などの最適な設計と 調整を行った。開発目標の垂直乗り越え段差 100μm、パターン寸法 5~10μm を 400℃以下、 10μm/min の成膜速度、1cm/min の描画速度を実現することを目的とした。また、既存のエアロゾル デポジション(AD)法やインクジェット技術、マイクロディスペンサー技術などのマスクレス成膜技術 を複合し、さらにノズルーワーク間での液滴、材料ジェットに対するレーザー加熱援用等を行うこと により高品位な膜形成を目指した。加えて原料ソースとなるナノインク、ナノペーストの最適化、高 度化を図り、最終的に微細、低抵抗で高周波領域、大電流領域で使用可能な線幅 100um 以下の 微細厚膜配線パターンをマスクレスで直接描画できるマテリアル・ダイレクト・ライティング(MDW)技 術を開発した。この技術に感光性ポリイミドや精密めっき金属などを用いた高密度 SI(半導体集 積) 実装技術と組み合わせて (a) MEMS-半導体、MEMS-MEMS 間のシールド構造を持った高密 度実装配線や、(b) MEMS センサ・アクチュエータ部材形成に必要なインターポーザ、フレキシブ ルな樹脂部材、金属部材を用いた場合の段差接続や曲面上での高密度配線、(c) 受動部品やセ ンサ、アクチュエータなど MEMS 部材を高密度な埋め込み一体化をカスタムメイドに実現できるオ ンデマンド性の高い MEMS 実装プロセスを開発した。

#### 2. レーザー援用インクジェット法の開発

#### 2.1. 背景

従来の配線技術との比較において、インクジェット法はいくつか課題が挙げられていた。大別すると現在実用化されているフォトリソグラフィ、スクリーン印刷等が生産現場では主に使用されている。これらの従来技術を比較すると、インクジェット技術の大きなの優位点と問題点が浮きぼりになる。そのなかで、インクジェット技術が持つおおよその優位点と問題点を列記する。

#### 優位点

- ・マスクレスかつ真空プロセスが必要なく、装置自体が安価。

- ・カスタムメイド、アドオンメイドに対応するための実装のフレキシビリティーを持つ。

- ・3 次元配線実装が可能。

#### 問題点

- ・配線工程において、他の技術よりインクジェットはスループットが大きく遅い。

- ・配線幅が30µm以下の描画が出来ない。さらに膜厚が薄く、低抵抗の配線を得られない。得

るためには、重ね塗り等が必要。

・描画精度を保つために、前処理が必要。

などがあげられる。このためこれらの点を留意しインクジェットの優位点を維持しつつ、問題点を解決するためには、インクジェットにおける本質的な問題点を抽出し、解決しなければならない。

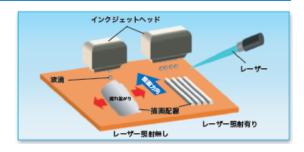

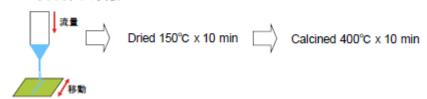

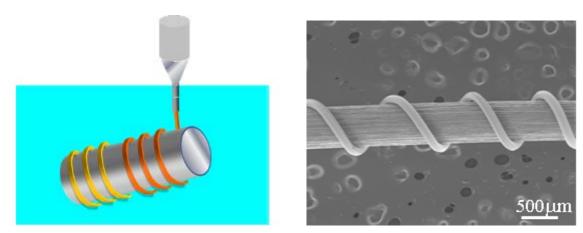

## 2.2. レーザー援用インクジェットシステム

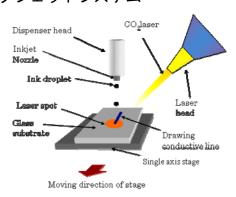

図 2-1. MDW 用のシングルヘッド圧電式微小液滴吐出装置と CO2 レーザー

実験装置は、図 2-1 に示すように簡易な構成とした。インクジェットヘッドは、任意の周波数および液滴径が吐出可能な圧電式シングルヘッドを用いた。エネルギーを援用するために、基本的には、各種レーザーの中で比較的安価な CO<sub>2</sub>レーザーを用いた。また使用した全ての基板において、撥水処理等の表面加工等は施していない。

#### 2.3. レーザー援用の効果

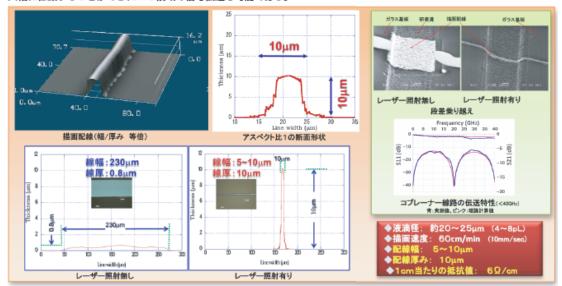

#### 2.3.1 液滴径 50μm を用いて配線を描画

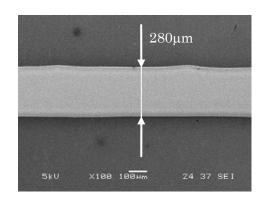

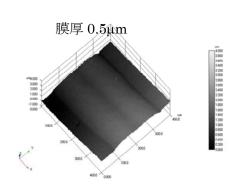

次に液滴径 50μm の場合、エネルギー援用が、描画配線に及ぼす効果について検証した。その結果、図 2-2 に示すように、レーザー援用の条件を最適化することにより、線幅 50μm、膜厚 2μm の配線を、24cm/min という速度で高速に描画することが可能となった。この結果からエネルギー援用により、配線幅を約 5 倍減少、膜厚を 4 倍と増加させることとなり、配線のアスペクト比(線幅:膜厚)は、20 倍改善された。また、レーザー照射した配線は、配線中央部に僅かな窪みがあることから、既知の現象と知られているコーヒーリング現象の影響を受けていることがわかる。

レーザー照射無し

レーザー照射有り

図 2-2. 液滴径 50µm を用いた場合のレーザー照射が配線形状に与える効果

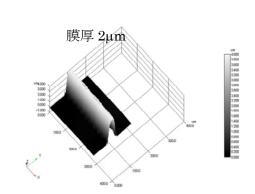

## 2.3.2 液滴径 25μm を用いて配線を描画

-10μm

レーザー照射無し

レーザー照射有り

ステージ速度: 60cm/min

アスペクト比 1:1の描画配線の3次元形状

図 2-3. 液滴径 25µm を用いた場合のレーザー照射が配線形状に与える効果

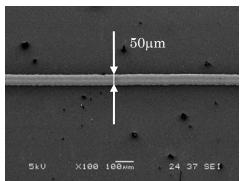

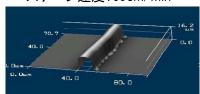

さらに上記の結果を踏まえて液滴径  $25\mu m$  を用いた場合、エネルギー援用による描画配線に与える効果について検討を行った。その結果、図 2-3 に示すように、配線幅は、 $7\sim10\mu m$ 、厚み  $10\mu m$ 、描画速度は、60cm/min と大幅に改善された。

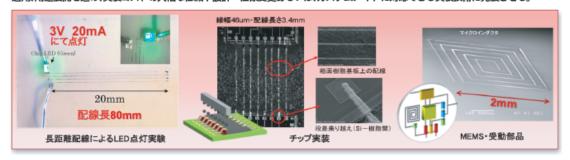

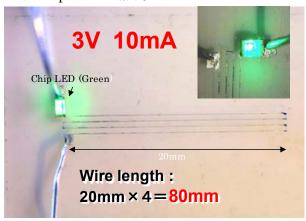

## 2.3.3 長距離配線による ChipLED の点灯

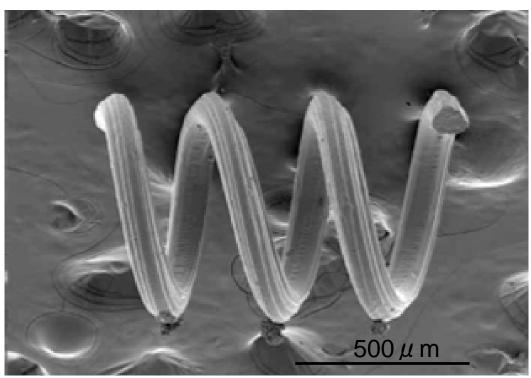

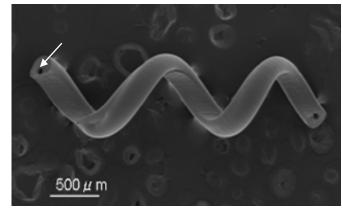

図 2-4. ジグザグ型長距離伝送線路による Chip LED の点灯実験 (LED 定格値 3V, 20mA)

この厚みのある配線形状と低抵抗値を持つ配線を長距離描画し、大電流を伝送できるかどうか Chip-LED (BW-191GR-CT, Bullwill. Co., Ltd.)を点灯させることにより実証した。まず、ガラス基板上に、ジグザグに配線を描画した。サイズと形状は、、線幅 40μm、配線厚み 2μm、20mm の配線を4 本ジグザグに描画し、約 80mm の配線長とした。そして、両端に ChipLED および電極を設置し Chip LED(定電圧:3V、定電流、20mA)に 3V、20mA を印加した。その結果、図 2-4 に示したように配線長 80mmの配線を用いても、問題なくLEDが点灯することが確認できた。このことから、エネルギー援用による配線は、従来のインクジェットによる配線と異なり、膜厚が高いため、単位長さ当たりの抵抗値が低くなることから、実用的であることが実証できた。

#### 2.4 直接描画実装配線技術の開発 -段差乗り越え直接描画配線技術の開発-

## 2.4.1 エネルギー援用効果が段差乗り越えに及ぼす影響

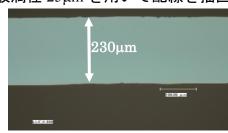

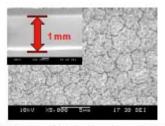

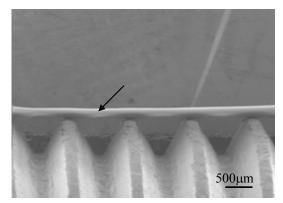

実際の段差乗り越えにおいて、基板表面や傾斜角度のすべてを制御することは困難である。そのため、ガラス基板に幅 1mm 程度、深さ 100~200μm 程度、傾斜角度 45~70°程度の溝を設置して、段差の上り下りが配線形状に及ぼす効果について確認を行った。その結果、図 2-5 に示すように、上り下りがあり、さらに傾斜角が大きく変わる部材に対しても問題なく描画できる事が確認された。

レーザー照射無し

レーザー照射有り

図 2-5. 溝幅:約 1mm、 段差:約 100~200μm 段差傾斜角:45~70 度 各段差傾斜角度による段差乗り越え

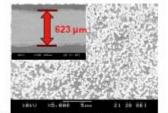

#### 2.4.2 段差エッヂ部

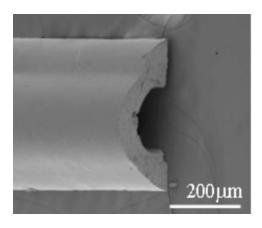

基板材質:Si、 段差 250µm、 段差傾斜角:56℃ 図 2-6. 段差エッヂ部の描画配線の形状

従来において、段差のエッジ部においては、配線を描画することが困難であった図 2-6 にシリコン描画した写真及びエッヂ部の拡大像を示す。この配線を描画したこのような結果から、レーザー援用の効果は、鋭利なエッヂ部でも数 μm 程度の十分に厚みのある配線を描画することが可能であった。

# 2.5. レーザー援用 MDW 法により直接描画したコプレナ伝送路の高周波伝送特性

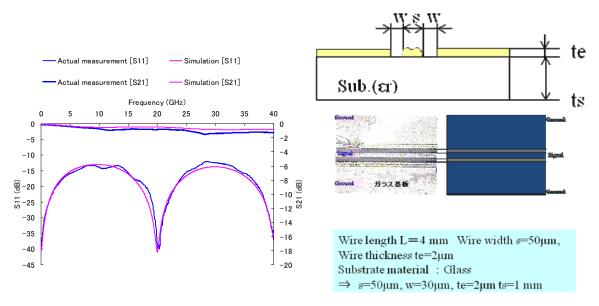

エネルギー援用インクジェット法により、ガラス基板上にコプレナ伝送線路を描画した。その後、作製した伝送線路の1から40GHzまで伝送特性をネットワークアナライザ(E8363C Agilent Technology)を用いて評価した。その結果を図 2-7 に示す。その結果、シミュレーションにとに近似した伝送特性と反射特性を得ることが出来た。

図 2-7. コプレナ伝送線路による 1-40GHz帯域の高周波伝送特性

#### 3. シールド線直接描画技術の開発

#### 3.1. はじめに

マテリアル・ダイレクト・ライティング(MDW)技術開発のためのLowK 誘電体層形成用原料ソー スに求められる特性は、(1)低粘度でノズルの根詰まりや膜質の不均質化を防止できること、(2)ノズ ルから吐出後は微細液滴となり、溶媒の揮発を促進してゾル中のセラミックナノ粒子の常温衝撃固 化現象を利用したMDW を可能にすること、(3)成膜後は多孔膜となり、誘電率を小さくできること などである。そこで、(1)ナノ粒子として誘電率が低いSiO2やSiO2-Al2O3系あるいはAD 法で常温 衝撃固化現象が確認されているPZT、BTO、Al<sub>2</sub>O3などを検討する。成膜後にSiO2、SiO2-Al<sub>2</sub>O3 及びAl<sub>2</sub>O<sub>3</sub>系では比誘電率で2~5 程度を、PZT 及びBTO 系では比誘電率で数十程度を達成 する。また、ナノ粒子表面の化学修飾を行い均質化と低粘度化を検討する。(2) ノズルからの吐出 後に液滴サイズが1µm 以下となる凝集ナノサイズゾルの開発。(3)成膜後の多孔化実現のため数 +nm のナノ粒子化を実現し、成膜後サブnm~数nm のナノポアを形成するゾル調製条件を確立 する。そして、数百nm~数μm の段差をカバーできるスロープをMDWで開発する。 ①スピンコート 法及びDMW 法によるLow-k誘電体層形成過程の調査:合成した前駆体ゾルの形成過程を半導 体製造技術で一般的なスピンコーターを用いたスピンコート法とマテリアル・ダイレクト・ライティング (MDW) 法とでどの様に異なるかを調査する。 基礎データとして、回転粘度計で測定した前駆体ゾ ルの粘度や乾燥・焼成速度(ランプ加熱による急速焼成)の影響を検討する。②形成したLow-k 誘電体層の評価(微構造と誘電率の関係):形成した誘電体層の誘電率と微構造との関係を評価 し、前駆体ゾルの特性や膜形成過程と誘電特性などとの関係を明確にする。そして、前駆体ゾル の分子構造などを赤外分光光度計などで評価する。し、抵抗率10<sup>12</sup>Ω·cm 程度、誘電率4 以下の 厚膜をスピンコート法またはMDW 法で電極付きSi ウエハー上に形成することを目標とする。

#### (H18 年度)

ゾル材料の目標として、シリコンウエハー上に形成後に抵抗率10<sup>12</sup>Ω・cm 程度、誘電率4以下となる厚膜用の材料を実現する。初年度はMDW法の装置などが間に合わないため、スピンコート法を中心に形成実験を行い、材料の微構造と誘電率の関係を評価する。MDW装置の進捗に併せ、MDW のテストも行い、スピンコート法との違いに付いて検討する。

#### (H19 年度)

H19 では、H18 に開発した材料を中心にMDW 法を用いた製膜を検討し、MDW法の場合にも抵抗率10<sup>12</sup>Ω・cm 程度、誘電率4 以下の厚膜を電極付きSi ウエハー上に形成できる前駆体ゾルの実現を目指す。MDW 法についても製膜過程や製膜後の微構造と誘電率の関係に付いて検討する。その際、卓上型ランプ加熱装置を用いて熱処理の効果を確認し、膜の誘電率を測定する場合に印加電圧の効果をバイポーラ電源を用いて電圧に対する誘電率変化を確認することでMDW 法用に最適な原料ゾルを実現する。

#### (H20 年度)

種々のゾルをインクジェット方式で吐出することを試みたが、ゾルの分子設計と粘度変化などの問題により最適なゾルを開発できていない。そこで、MDW用原料ゾルの開発には、超音波霧化などのインクジェット法以外の方法も検討する。そして、それぞれの方法にあった原料ゾルの開発を試

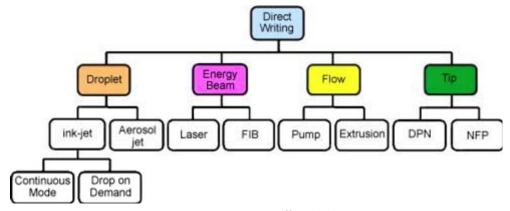

みる。最終的に、MDW 法の場合にも抵抗率10<sup>12</sup>Ω·cm 程度、誘電率4 以下の厚膜を電極付き Si ウエハー上に形成できる前駆体ゾルを実現する。以上のことから、本年度はMDW に適したインクジェット法以外の方法の検討を中心に行った。最初に、前年度までの研究で開発したシリカーアルミナ系ゾルを用いた超音波霧化を検討したが、粘度が高すぎるために霧化ができなかった。そこで、超音波霧化法以外の手法で年度がある程度高いスラリーでもMDW 可能な方法を検討した。MDW に用いることができる手法としては、図3-1のような大きく分けて4 つの手法が考えられる。すなわち、①インクジェットやエアロゾルでポジション法のようなドロップレットを生成させる方法、②レーザーやイオンビームを用いる方法、③ポンプなどを用いた細いニードルからの押し出しなど、④チップを用いたDPN やNFP、である。このうち、スラリーを用いた方法では一加算の手法を用いることとなる。一の手法については本研究グループの静大以外のグループが主に担当していることから、③の手法によるMDW を試みた。その際、押し出される原料スラリーの幅を小さくするために、電界の印加を用いたエレクトロスプレイ法を検討したので報告する。この方法では、ポンプなどにより強制的に押し出されたドロップレットに電界を印加することで、比較的粘度が高い原料スラリーを用いても比較的細い描画が可能となるものと期待される。

図3-1. Direct wiring 技術の分類

#### 3.2. ムライト前駆体溶液の調製

#### 3.2.1. はじめに

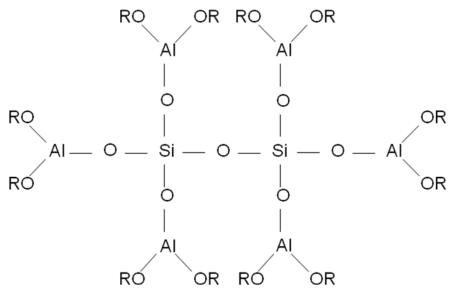

金属アルコキシドを原料としてムライトを調製するために、Si アルコキシドとAl アルコキシドを使用するが、この2つのアルコキシドは加水分解速度が著しく異なる。このことを考慮してSiアルコキシドとAlアルコキシドを均一に共重合させムライト前駆体溶液を調製する必要がある。この方法として鈴木らが考案したSi-Al ダブルアルコキシド法がある。これはSi、Al の加水分解速度を考慮し分子設計された目的の化合物を得るのに画期的な方法である。すなわち、Si アルコキシド、Si(OR)4 はAl アルコキシド、Al(OR)3 に比べて加水分解速度が遅いため、あらかじめ部分的に加水分解を行う(部分加水分解法)。一方Alアルコキシドは加水分解速度が著しく速いため側鎖基を部分的に立体障害が大きい基に置換して優先的に加水分解されやすい位置をつくったのち、部分的に加水分解したSi アルコキシドと共重合反応させることによって高均質前駆体溶液(ダブルアルコキシド)を調製した。この前駆体アルコキシドを加水分解、仮焼することによって高純度、高均質で化学量論組成のムライト微粉体が得られる。理想的な反応式を式(3-1)に示す。

$$SinOn-1(OR,OH)2n+2+Al(OR)3 (n=2)$$

(3-1)

Si アルコキシド (SiOR)<sub>4</sub> + Al アルコキシド Al(OR)<sub>3</sub> 共重合 ムライト

図 3-2. 前駆体アルコキシドームライトの反応式

## 3.2.2. 実験方法

高均質ムライト前駆体溶液の作製に用いた試薬を以下に示す。

- ① オルトケイ酸エチル (TEOS:Si(OC2H5)4), Tetraethyl Orthosilicate 和光純薬株式会社製 試薬特級 純度 > 95.0%

- ② アルミニウムイソプロポキシド (AIP:Al(OCH(CH3)2)3), Aluminium Isopropoxide東京化成工業株式会社製

- ③ エタノール(EtOH:C2H5OH), ethanol 関東化学株式会社製 試薬特級 純度>99.5%

- ④ イソブタノール(i-BuOH:(CH3)2CHCH2OH), Isobutyl Alcoholナカライテク株式会社製 試薬 特級 純度>99.0%

- ⑤ 塩酸(HCl), Hydrochloric Acid関 東化学株式会社製 試薬特級 塩化水素36%

なお、エタノールは表記した試薬を脱水するという操作を実験室で行い、さらに純度を高くしたも のを用いる。

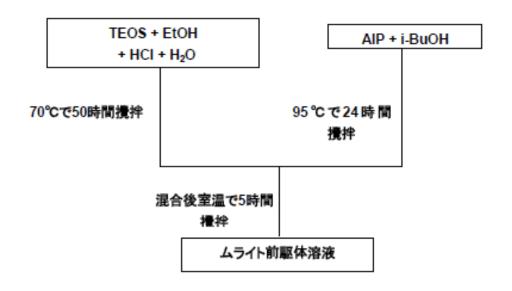

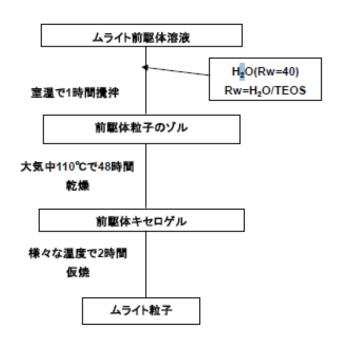

図 3-3. ムライト前駆体溶液調整方法

本研究ではすでに報告されている調製方法を参考にし、ムライト前駆体溶液を調製した。常温でTEOS をエタノールに濃度が1mol/dm3 になるように混合した後、攪拌しながら蒸留水と塩酸を滴下し、70℃で50時間反応させることによってTEOSの部分加水分解溶液(Si溶液)を調製した。なお、それぞれの濃度はH2O/TEOS=2mol/mol , HCl/TEOS=0.1mol/mol とした。次にイソブタノール中に濃度が1mol/dm3 になるようにAIP粉末を加え、95℃で24時間攪拌することによってAIP溶液(AI 溶液)を調製した。このように調製したAI溶液にSi溶液を室温まで冷ましてから液量3:1の比で常温で混合し、5時間攪拌することによって共重合させ、淡い黄色の透明なムライト前駆体溶液を調製した。図3-3に調製方法のフローチャートを示す。

## 3.3. ムライト系多孔質ナノ粒子粉体の作製

#### 3.3.1. 実験方法

この実験では得られるムライト系多孔質粒子の比表面積が最も高くなるような条件で実験を行っている。この条件は過去の論文にムライト微粉体の比表面積に及ぼす加水分解条件の影響について報告している論文があるのでそちらを参考にしている。まず図3-3において得られたムライト前駆体溶液にTEOS に対して40 倍mol 量の蒸留水(Rw=H<sub>2</sub>O/TEOS=40)を加え1時間攪拌させる。この蒸留水を加えたときに一時的に粘度が増すのでしばらくはガラス棒等で激しく攪拌させなければならない。攪拌後、得られた前駆体ゾルを110℃にて48 時間乾燥させ前駆体キセロゲル微粉体を作製した。このムライト前駆体キセロゲルを様々な温度(400、800、1000、1300℃)で仮焼することにより、仮焼温度が及ぼす比表面積への影響とどの程度の温度でムライト相が観察されるかを調べた。なお、昇温速度は10℃/min とした。図3-4にここまでの一連の操作をフローチャートにまとめる。

図 3-4. 前駆体溶液からのムライト粒子作製方法

## 3.3.2. 評価方法

#### (1) XRD による結晶相の同定

仮焼温度の異なるそれぞれのムライト仮焼粉体をアルミナの乳鉢を用いて細かく粉砕し、XRD 測定用試料ホルダーにセットしCuKα線を用いて、20 度から70 度までのXRD パターンを測定し、 そこから結晶相の同定を行った。

#### 【測定装置】

形式: 粉末X 線回折装置

機種: RINT2200

製造会社:理学電気株式会社

#### 【測定条件】

X線源:CuKα 印加電圧:40kV

電流:20mA

走査速度:4deg(2θ)/min ステップ角度:0.02deg

#### (2) 比表面積の測定

仮焼温度の異なるそれぞれのムライト仮焼粉体をアルミナの乳鉢を用いて細かく粉砕し、この試料をあらかじめ200℃で真空排気し液体窒素温度で窒素を吸着させ、その脱離量からBET比表面積を求めた。以下に測定装置を示す。

#### 【測定装置】

## 名称:窒素吸着比表面積測定装置

型式:ASAP2010

製造会社: 島津製作所株式会社

#### 3.3.3. 結果および考察

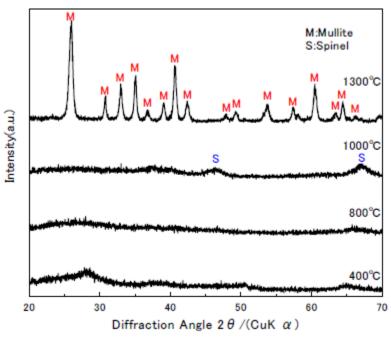

#### (1) XRD による測定結果

さまざまな温度(400~1300°C)で2 時間仮焼したムライト前駆体キセロゲル(以下ムライト系微粉体)のXRD パターンを図3-5に示す。図3-5からこの粉体が1000°C以下の仮焼温度ではほぼ非晶質であるということがわかる。1000°C付近からだんだんとスピネル相が現れはじめ、1300°Cでこのムライト系微粉体が完全にムライト相となった。ムライト相以外のピークが観測されないため、この実験で調整した粉体は非常に高均質であると思われる。

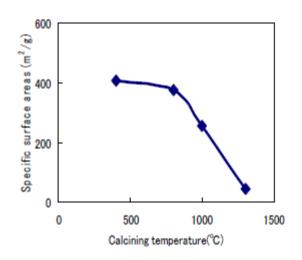

#### (2) 比表面積の測定

ムライト微粉体のさまざまな仮焼温度(400~1300℃)による比表面積の変化の測定結果を図3-6に示す。この図3-6からこの微粉体の比表面積が800℃付近を境に急激に小さくなっていることが読み取れる。仮焼温度に伴う比表面積変化は以下のような過程で起こるものと考えられている。ムライト系微粉体を加熱していくと800℃付近まで残存する有機物の蒸発、分解に伴う前駆体粒子の収縮および緻密化によって比表面積は減少する。そして前駆体からスピネル相あるいは斜方相系のムライト相への結晶化に伴う体積収縮と粒成長によって800℃以上の温度によって急速に比表面積は減少したと思われる。もっと高温で焼結させたもののデータをとれば明らかになるが、すでに完全にムライトへ結晶化してしまった1300℃以上ではおそらく大きな比表面積変化はないであろう。

図 3-5. XRD によるムライト微粉体結晶相の同定

図 3-6. 異なる仮焼温度による比表面積変化

## 3.4. 多孔質ムライト系原料スラリーの作製

#### 3.4.1. 遊星ミルによるムライト系微粒子分散溶液の作製

#### (1) 実験方法

ムライト系微粒子を薄膜化するにあたってまず何らかの形で液体中に分散させなければならない。ムライトセラミックスというものはシリカ-アルミナ系において最も熱的、化学的に安定な酸化物の一つであるので本実験では物理的に分散させようと遊星ミルを用いた。分散溶媒には1-ブタノールを使い、今回は多孔質薄膜の作製を目的としているため、高比表面積を有し、さらに有機物などの不純物がある程度焼き飛ばされていると考えられる800℃で仮焼したムライト系微粒子を溶媒に濃度が1wt%、3 wt%、5 wt%になるように調製したのち遊星ミル専用ジルコニア容器にジルコニアボール50gとともに入れ、遊星ミルにセットし回転数500rpmに設定し2時間解砕、分散を行った。以下にこの実験で使用した器具、試薬を示す。

- 1. 1-ブタノール (CH3(CH2)2CH2OH) , 1-Butanol 関東化学株式会社製 試薬特級 純度>99.0%

- 2. 遊星ミル形式:遊星型 微粒粉砕機機種:P-7 (FRITSCH)

- 3. ジルコニアボール (ZrO4) 直径 0.3mm 密度 5.7g/cm3 純度>95.0%

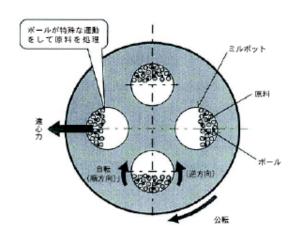

#### ※ 遊星ミルの原理

遊星ミルは図3-7に示すとおり公転するミル公転体と順方向または逆方向に自転するミルポットの中に粉砕媒体(小径ボール)と処理粉体を入れ、ミルポットを公転・自転運動すなわち遊星運動させることにより、ボールに大きな遠心加速度と特殊な運動を与えて粉体を処理する。小さい直径のボールを使用すると、単位体積あたりのボールの個数が多くなり、ボール間で粉体を処理するチャンスが飛躍的に多くなる。たとえば、直径が半分になるとボール個数は約8倍になるので、粉体を均質に処理することができる。直径が小さく1個あたりの重量は少なくなるが、大きな遠心加速度を

与えることにより小径ボールが持つエネルギーを、遠心加速度の小さい大径ボールと同程度にすることができるので短時間で均質な処理が可能となる。これが遠心加速度を大きくする利点である。

図 3-7 遊星ミルの原理

粉砕に関する一般的な緒言として以下の事が挙げられる。

- ・粉砕時間・・・時間をかければかけるほど粒度は細かくなる。

- ・回転数・・・回転数が高いほど粉砕時間は短縮され、粒度は細かくなる。

- ・ボールの数量及び大きさ・・・比較的大きな、硬い試料には比較的大きなボールで前粉 砕すればより細かな粒子となる。径の小さなボールを数多く 使い、粉砕時間を長くすれば粒度は細かくなる。

- ・ボールの密度・・・ボールの密度が高いほど、粉砕効果も高くなる。

## 3.4.2. 評価方法

#### (1) 粒度分布の測定

まず粒度分布測定に使用した測定装置を示す。

#### 【測定装置】

形式:電気泳動光散乱光度計 機種:ELS-800 LEZA-600 製造会社:大塚電子株式会社

各濃度の分散溶液を用いて、濃度差による解砕する粒子への影響、さらに0、24、48 時間後毎に測定し、時間経過による粒子の凝集を調べる。粒度分布を測定する理由として以下のことが挙げられる。

① どの程度の粒子が溶媒に分散し、薄膜を形成しているのかを調べる。

- ② 同じ条件で再度分散を行ったとして、常に安定な微粒子の分散、粒径が確認できるか。

- ③ 時間経過毎の粒径を測定することによって凝集性の確認をし、工業化を考えたとき作製した分散溶液が安定的で保存に優れているかを確認する。

以上の点を念頭に置き、粒度分布の測定をした。

#### (2) 粘度の測定

各濃度の分散溶液を1ml とり、測定機器にセットし粘度を測定した。さらに時間経過(0、24、48時間後)による粘度変化への影響も調べた。以下に本測定で使用した粘度計を示す。

#### 【測定装置】

形式:回転式粘度計 機種:RE80L MODEL

回転に使用したローター:1°34'×R24 製造会社: 東機産業株式会社

#### 3.5. 粒径 50nmSiO<sub>2</sub> シリカ溶液の作製

#### 3.5.1. 実験方法

本実験で使用した粒径が50nm の $SiO_2$ シリカ分散溶液の調製方法、および作製したシリカ粒子の具体的粒径サイズを以下に示す。 $SiO_2$ を作製する際、触媒として酸触媒を使用すると縮合反応段階で線状の $SiO_2$ ができ、塩基触媒を使用すると粒子状の $SiO_2$ ができることが知られている。本実験では粒子状の $SiO_2$ を用いるため塩基触媒としてアンモニア水を用いた。以下に作製に使用した試薬を示す。

- ① オルトケイ酸エチル (TEOS:Si(OC2H5)4), Tetraethyl Orthosilicate和光純薬株式会社製 試薬特級 純度 > 95.0%

- ② エタノール(EtOH:C2H5OH), ethanol関東化学株式会社製 試薬特級 純度>99.5%

- ③ アンモニア水 (NH3), Ammonia Solution和光純薬株式会社 試薬特級

NH3 25%シリカ粒子のサイズはTEOS とアンモニアのモル混合比により制御できる。50nm のシリカ粒子を得るにはTEOS/NH3=0.450mol/ mol となるように混合し、さらに蒸留水をH2O/TEOS=2mol/mol を加える。最後に全量200ml になるようにエタノールを加え、30℃で72 時間攪拌させることによって[エタノール溶媒、粒径50nm、0.3mol/l]のシリカ溶液を得た。図3-8に実際測定したこの溶液に分散しているシリカ粒子の粒径を示す。

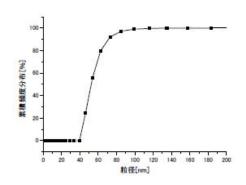

図 3-8. 調整した SiO2 シリカ粒子の粒径サイズ

#### 3.6. 前駆体溶液の作製

ムライト前駆体溶液は空気中に放置しておくと、大気中の水分により加水分解し容易に凝固してしまう。この前駆体溶液を溶液のまま使用するためには、側鎖基であるOH 基を何らかの形に置換し安定化させる操作が必要となる。今回安定化にはアセチルアセトンを使用した。本実験では前駆体溶液のAl に対して等倍mol のアセチルアセトンを加えた。

## 3.6.1. 評価方法

### (1) 走査型電子顕微鏡(SEM)による薄膜の膜厚測定

作製した5 種類の基板についてSEM により断面を観察し、断面図から膜厚を同定した。以下に使用した機器を示す。

【測定装置】名称:SEM 機種:JSM-5600 製造会社:日本電子株式会社

#### (2) 原子間力顕微鏡(AFM)による表面観察

作製した5 種類の基板についてAFM により表面を観察した。本研究をLTCC(低温同時焼成セラミック)へ応用することを視野に入れた場合、表面は非常に綿密でなければならない。今回AFM は表面の細かい形状や輪郭を観察するのに優れる誤差信号像で測定した。以下に使用した機器を示す。

【測定装置】名称:AFM 機種:SPI3800N 製造会社:セイコーインスツルメンツ株式会社 【測定条件】スキャナ:20nm スキャナカンチレバー:SI-DF3-R

## 3.6.2. 結果および考察

#### (1) 粒度分布測定結果

まず以下に図3-9に粒度分布測定結果を示す。

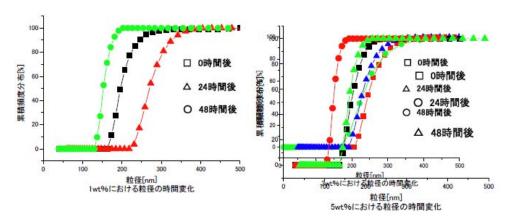

図 3-9. 角濃度の時間経過における粒径変化

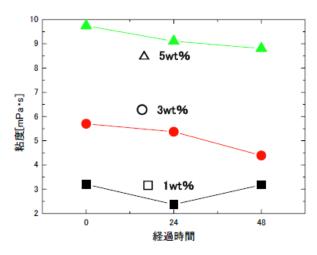

図 3-10. 時間経過における粘度変化

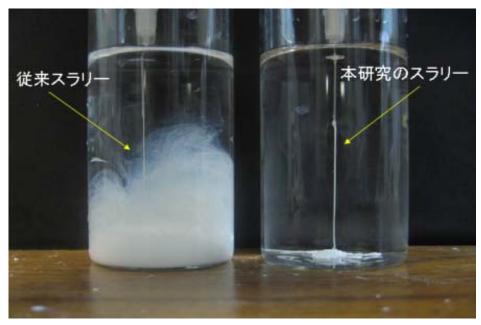

濃度が濃くなるにつれ粘度が高くなることが示された。さらに時間経過における粘度は各濃度とも小さくなっている傾向が見て取れる。時間経過によって粒子が凝集挙動を示すのであれば、粘度は増加傾向をとるはずである。減少傾向にあるということは粒子が沈降状態にあると考えられる。時間経過により大きな粒子は沈降し、溶液の上層では分散させた粒子の濃度が低下しており、結果として図3-10のような減少傾向を示したと考えられる。本測定結果と先の粒度分布測定結果から、ムライト分散溶液の濃度は5wt%が妥当だと思われる。すなわち、1、3、5wt%で粒径が変わらないのであれば、薄膜を作製する際、少ない積層数で目的の膜厚を達成するにはより高濃度のものが適しているという理由から5wt%が最適であると考えた。なお、次の章で述べるエレクトロスプレイ法によるMDWを7wt%の原料スラリーでも試みたが、この場合は粘度が高くなりすぎてMDWができなかった。

# 3.7. エレクトロスプレイ法によるアルミニウムあるいはニッケル箔上への MDW

## 3.7.1 はじめに

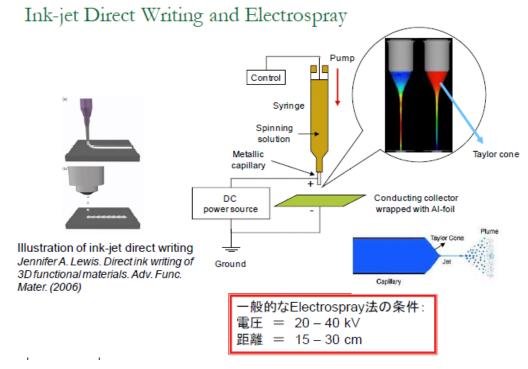

MDWを達成する手法として大きく二つの手法があることはすでに述べた。ここでは、エレクトロスプレイ法の概略をインクジェット法と比較して示す。(図3-11)

図 3-11. エレクトロスプレイ法

electrohydrodynamic spray (electrospray) method

電界を印加すると表面張力 が減少する

Taylor-cone型

Several illustrations of drop formation. (a) Dripping (b) Jetting (c) Electrohydrodynamic (d) CIJ (e) Piezo-DOD (f) TIJ-DOD (g) Flow focus (h) Aerosol Jet (i) Tip Basaran, OA. Small-scale free surface flows with breakup: Drop formation and Emerging Application. AIChE Journal (2002)

図 3-12. エレクトロスプレイ法により吐出するドロップレットの様子

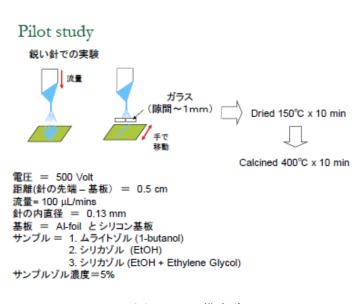

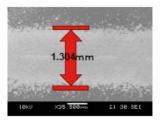

エレクトロスプレイ法では、インクジェット法よりも多様なスラリーを用いることができる反面、線幅を小さくすることが困難であるという特徴がある。そこで、ある程度高濃度で粘度が高いスラリーでもMDW が可能なエレクトロスプレイ法でムライトあるいはシリカナノ粒子からなるスラリーを用いて線幅を細くする条件を検討した。図 3-12 はエレクトロスプレイ法により吐出するドロップレットの様子がエレクトロスプレイの際のスリットの有無や基板との距離あるいは電界強度によってどの様な影響があるかを模式的に示したものである。エレクトロスプレイ法では、スラリーに電界を印加することよって表面張力が減少し、マイクロドロップレットが生成する。そのサイズはスラリーの粘度や電界強度に依存する。そこで、図 3-13 のような条件で予備実験を行った。その結果得られた MDW によるラインの SEM 写真を図 3-14 示す。基板をアルミニウムホイルとした場合でも Si 基板を用いた場合でも、先端が斜めにカットされた吐出用のニードルを用いた場合には、吐出されたドロップレットが拡散してしまい、スリットを入れたガラスカバーを用いてエレクトロスプレイ法によっても線幅 1mmを超えてしまった。そこで以降の実験では先端をフラットにカットして電界をニードルの中心付近に集中することで、均一な細線 MDW できる条件を検討した。

図 3-13. 予備実験

Mullite deposited on Al-Foil by electrospray + glass cover

Mullite deposited on silicon-substrate by electrospray + glass cover 図 3-14. 実験結果

## 3.7.2 吐出流量が線幅に与える影響

予備実験の結果から、先端がフラットにカットしてあるニードルを用いてスリット入りカバーガラスを用いることなくMDWをした場合の線幅に与えるトスラリー吐出流量の影響を検討した。用いたマイクロシリンジと電界印加用の直流電源を図3-15に示す。用いた基板はニッケル泊である。また、スラリー中のムライトナノ粒子の濃度は5%とした。印加電圧はやはり予備実験の結果から400V~600Vの範囲で行った。スラリー流量により電流値が変化するため、この範囲の電圧で電流値を一定にしてエレクトロスプレイによるMDWを試みた。ニードルの内径は130μmで基板移動速度は予備実験の結果から1mm/min.とした。そして、吐出流量は5~100μL/min.でMDWを行った。Ni 箔の厚さは50μmのものを用いた。

## Sample Deposition (mullite sols 5% in 1-BuOH)

図 3-15. マイクロシリンジと電界印加用の直流電源

\*\* Worker Bee Syringe, Bioanalytical System Inc.

\*\*\*Hamilton Company

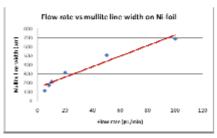

吐出流量を100μL/min.から少なくして行くと生成するラインの幅は次第に細くなり、5μL/min.の吐出流量では約100μmまで細線化することが可能であった。さらに吐出流量を少なくすることで100μm以下の細線をMDWで直接描画することも可能であると思われた。そして、ガラススリットを用いることなくエレクトロスプレイした場合でも、先端がフラットカットされたニードルの使用により中心部で電界集中が起こり、両端が明瞭なラインの描画が可能であった。ムライトゾルの濃度を5%としたが、スラリー濃度を低くすることでも線幅の制御が可能であると思われた。生成したラインの微構造は、ムライトゾルが若干凝集していたためにポアが生成したと思われた。適当な分散剤の使用によりこの問題を解決する必要があると判断した。

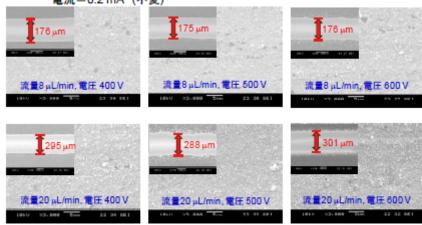

#### 3.7.3. 印加電圧が線幅に与える影響

次に、印加電圧が線幅に与える影響を吐出流量 8μL/min と20μL/min で一定にして検討した。 その結果を図 3-16 に示す。条件はほぼ前述と同様である。結果として、図から明らかなようにどちらの吐出流量を用いた場合にも線幅に大きな影響はなかった。すなわち、エレクトロスプレイが可能な印加電圧の範囲内であれば印加電圧の影響はほとんどないと言うことになる。

## Mullite line due to voltage

注意: 電圧の値は電源のツマミにより400 V~600 V とした

- < 400 V 針先で液滴のまま

- > 600 V 針先から拡散してしまう

電流=0.2 mA (不変)

図 3-16. 実験結果

#### 3.7.4. ITO 透明電極基板上での MDW

図3-8には、基板をITO 透明電極付きのガラスに変更した場合に吐出流量がMDW後の線幅に与える影響を示した。図から明らかなように、基板をITO 透明導電膜を塗布したガラス基板としてもMDW が可能であった。さらに、吐出流量が最もMDW 後の線幅に影響を与え、その線幅はニッケル箔上でもITO 付きガラス基板上でもほぼ同じであった。すなわち、この方法では基板に導電性があればエレクトロスプレイ法によるMDW が可能であり、その生成物の線幅は基板に依存しないと思われた。また、ガラス基板上へのMDWで得られたラインの方が若干緻密であるように思われた。これらの事実は、例えばインクジェット法で微細な電極配線パターンを作製したのち、エレクトロ

スプレイ法で導電性線の上だけに絶縁性パターンを形成できる可能性を示している。

##

## Mullite line width due to flow rate (on ITO Glass)

Fig.4-8

図3-17. 実験結果

## 3.7.5. シリカゾルを用いた MDW

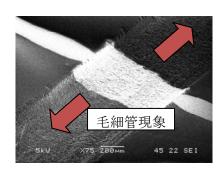

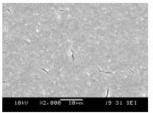

最後に、ムライトスラリーではなくシリカ単分散粒子からなるスラリーを用いてエレクトロスプレイ法による絶縁パターンのMDW に関する基礎的実験を行った。実験条件などは図3-18に示した。また、結果を図3-19に示した。図から明らかなように、シリカゾルを用いた場合エレクトロスプレイ法によるラインパターンはかなり粗いものとなった。この理由は現在までのところ不明である。しかしながら、シリカ単分散ゾルの凝集挙動と関係があるものと思われる。すなわち、シリカ単分散ゾルではムライト系スラリーと異なり大きさが均一でエレクトロスプレイの際に溶媒が蒸発するために横毛管力の影響を大きく受け、ライン形成後に微構造としてドメイン構造が残存したものと思われる。今後、この様な状況の改善のためにシリカ単分散ゾルの化学修飾が必要となると思われる。

## Sample Deposition (silica sols 220 nm)

#### フラット針での実験

電圧 = 400V (電流 0.2mA) 距離(針の先端 - 基板) = 0.2 - 0.5 cm 針の内直径 = 0.13 mm 基板移動速度 = 1 mm/sec 流量 = 100 μL/min 基板 = Aluminium foil

サンブル=シリカゾル 220 nm in Ethanol (RAW) シリカゾル 220 nm in 1-Butanol 溶媒を交換

Fig.4-9

図 3-18. 実験条件

SEM images of silica (dispersed in ethanol) deposited on Al-Foil by electrospray

SEM images of silica (dispersed in 1-butanol) deposited on Al-Foil by electrospray

原因としては、溶媒の基盤への濡れ性の違いが考えられる

原因としては、溶媒の蒸発速度の違いが考えられる

図 3-19. 実験結果

## 3.8. まとめ

ムライト系スラリー及びシリカ単分散ゾルを用いてエレクトロスプレイ法によりライン形成を試みた。 その結果、以下のような結論が得られた。

- ① 7% 濃度のムライトスラリーは、粘度が高すぎるためスプレイできない。

- ② 実験動作電圧は、400 V~600 Vが適当であった。

- ④ 実験動作電圧は形成する線幅にはほとんど影響がない。

- ⑤ 印加電圧が低いほど線の形状がきれいになる傾向が認められた。

- ⑥ 吐出流量が少ないほど、形成される線幅も狭くなる。

- ⑦ シリカゾルを用いたエレクトロスプレイ法では、ドメイン構造が形成されるために緻密な膜とならなかった。

- ⑧ エレクトロスプレイ法では基板とスラリーのぬれ性や溶媒の蒸発速度に大きく影響された。

## 4. 直接描画アドバンスド LTCC 技術の開発 -MDW用マイクロデスペンス用ナノスラリー調製技術の開発-

#### 4.1. 研究目的

高い流動性を有するとともに、ノズル通過後には迅速に固化するナノスラリーの調製技術を開発する。

### 4.2. 研究概要

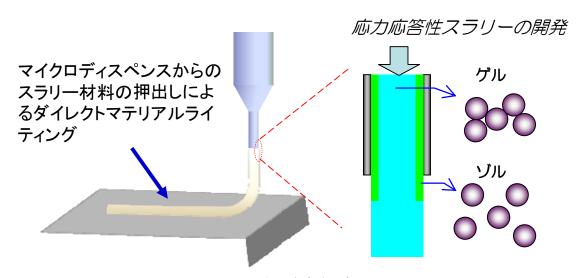

ナノスラリーの流動性発現に関する系統的な検討を行うことにより、MDW用ナノスラリー調製技術を開発する。ノズル通過時の力学的作用によるスラリーの高流動化とノズル通過後の構造回復によるスラリーの高粘性化等によるスラリー固化現象の検討を行う。また、熱分析装置によるナノスラリー材料の熱分解挙動の調査や雰囲気制御型電気炉を用いた成形体の熱処理プロセスの検討も行い、成形性と熱処理プロセスの観点からスラリー組成物の最適化をはかる。図4-1に本研究内容の概要を示す。

#### 4.3. 研究内容

## (1) ナノスラリー流動性制御技術の開発

ナノスラリーについて、力学的作用の変化によるスラリー流動性の迅速な変化を実現し、低せん断域と高せん断域でのスラリー粘度比が5以上を達成する。

#### (2) MDW 用ナノスラリー調製技術の開発

MDW用ナノスラリーについて、スラリー固化による直接描画を実現し、パターン線幅変動が 5%以下を達成する。

図 4-1. 本研究内容の概要

## 4.4. ナノスラリー流動性制御技術の開発

## 4.4.1. スラリー流動性の検討

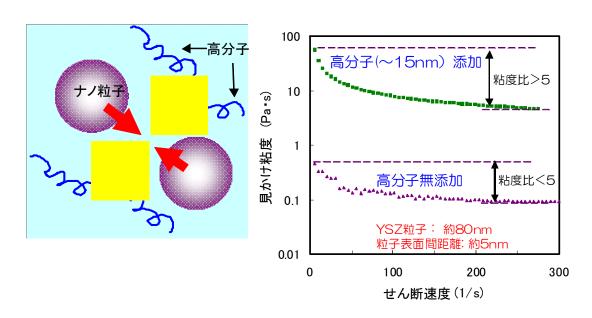

力学的作用の変化によって流動性の迅速な変化を発現するナノスラリーを開発した。このナノスラリーはコロイドゲルであって、せん断速度の増加とともに見かけ粘度が減少し、せん断力から解放されると再びゲル化する、ずり流動化流動を有するものである。本研究ではナノ粒子分散スラリーに適用可能な新しいコロイドゲル化法を開発し、目標である低せん断域と高せん断域でのスラリー粘度比>5を達成した。

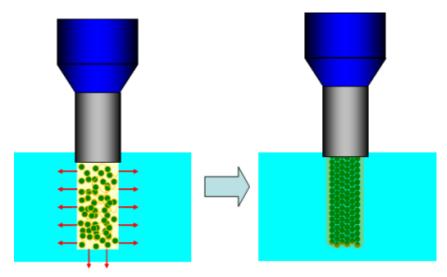

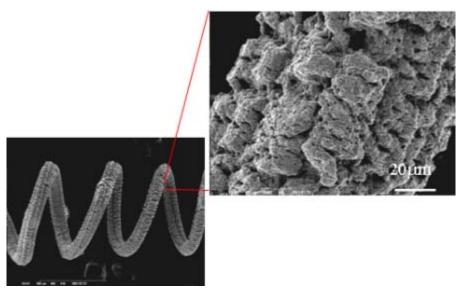

図 4-1 に示したように、MDW ではノズルから押出されたスラリーは迅速に固化しなければならない。コロイドゲル(粘弾性スラリー)はそれを可能にする。これは無機質のナノ粒子同士が凝集によって網目構造(ナノ粒子架橋)を形成したものである。ノズル壁面近傍ではせん断応力が加わり、ゲル状態(固化)からゾル状態(流動)に転移し、ノズル通過時には流動性となる(図 4-1: ノズル壁近傍の緑の部分)。一方、ノズルから押出されるとせん断応力は加わらないためゾル→ゲル転移が生じて、迅速に固化する。

本研究のコロイドゲル化法を、図 4-2 を用いて説明する。濃厚系のナノ粒子分散系に可溶な高分子を添加する( $\Box$ この高分子それ自体で溶媒をゲル化するものではない)。もし高分子が分散ナノ粒子間にサイズ効果的に入ることができなければ、粒子間の溶媒が浸透圧によって流出し(図 4-2:黄色)、結果として粒子間に引力が作用する(図 4-2:赤色)。詳細な計算によると、高分子が溶媒中に分散してナノ粒子同士が架橋した方がエントロピー的に有利となる。界面活性剤の進歩により、平均的な分散ナノ粒子の表面間距離は 10nm を容易に下回ることができるため、 $10\sim20$ nm 程度の高分子を添加すれば、図 4-2 の状態を実現できる。本研究では、ナノ粒子のサイズが 100nm 程度以下に対して、このエントロピー効果によってコロイドゲル化することを見出した(図 4-3 参照)。

図 4-2. 本研究のゲル化

図 4-3. ナノ粒子分散系における高分子添加の効果

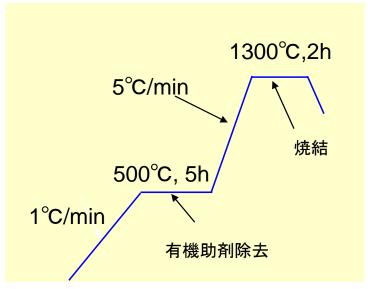

## 4.4.2. スラリー材料の熱分析

スラリー作製に用いた材料を表4-2に示す。分散剤、高分子そして可塑剤はセラミックス製造プロセスで典型的に使用されている材料である。熱分析の結果、それらの大気中での酸化分解温度は、約380℃、約400℃、約320℃であった。これらの添加量の総量はナノ粒子に対して高々5mass%程度しか加えてない。そのため、通常の脱バインダー、焼成プロファイルを用いて新規コロイドゲルによって得られたコロイド構造体を焼結することができた(図4-4)。

表4-2. 本研究で用いたスラリー材料

| ナノ粒子     | 溶媒    | 分散剤       | 高分子(バインダー) | 可塑剤      |

|----------|-------|-----------|------------|----------|

| YSZ 80nm | エタノール | ポリエチレンイミン | ポリビニルブチラール | フタル酸ジブチル |

|          |       | (PEI)     | (PVB)      | (DBP)    |

図4-4. 本研究で得られた焼結体

## 4.5. MDW 用ナノスラリー調製技術の開発

## 4.5.1. スラリー固化の検討

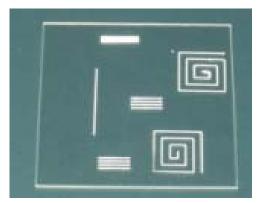

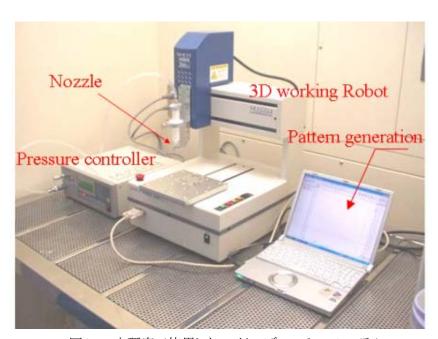

4.4節で示したコロイドゲルを用いて、大気中押出しにおけるスラリー固化によってダイレクトライティングが可能であること示した。ここではノズル径:200mm、押出しスピード:約1mm/sとしたときの結果について示す。図4-5に得られたコロイド構造体を示す。矢印で示したものが、エタノールが乾燥除去されたコロイド構造体である。コロイドゲルは凹凸表面上に押出されたが、乾燥した構造体は自己支持可能な強度(保形性)を有する。図4-6は一辺5cmの石英基板上にダイレクトライティングしたものである。なお、本実験では図4-7に示したシステムを使用した。これは3次元描画ロボット、ノズルおよび加圧系、そしてパターン形成用のPCから構成される。

図4-5. 凹凸表面上へのダイレクトライティング

図4-6. 石英基板上へのダイレクトライティング

図4-7. 本研究で使用したマイクロディスペンスシステム

このスラリーは溶媒乾燥を伴う。適切な濃度と溶媒乾燥速度を制御することにより、粒子移動に伴

#### う自発的なマイクロチャネル形成も可能である

図4-8. マイクロチャネル形成①

図4-9. マイクロチャネル形成②

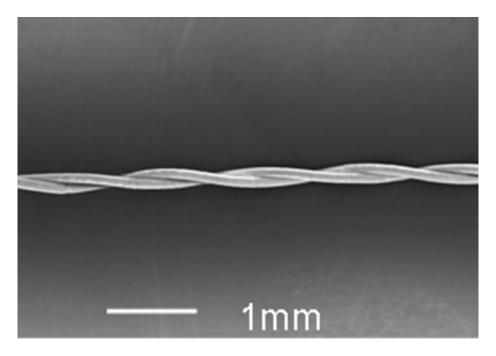

今回開発したスラリーは水溶媒中でのスラリー固化も可能である。水中ではエタノール溶媒の乾燥速度をより遅くすることができるため、ノズル詰まりの発生は効果的に抑制された。この水溶媒乾燥の原理を図4-10に示す。添加したPVBはエタノールには可溶で、水には不溶である。一方、エタノールと水は互いに良く混和するため、スラリー中からエタノールのみが水中へ拡散していき、このスラリーは水中で乾燥収縮される。結果として、PVBコーティングされたスラリー固化体が形成される(図4-11参照)。この現象を利用して作製したコロイド構造物の例を図4-12に示す。この現象を利用すると、スラリーの紡糸も可能となり、図4-13に示すようなフレキシブルに編んだコロイド構造体も形成できる。

図4-10. PVB/エタノール系スラリーの水中固化現象

図4-11. 本研究で見出された水中でのスラリー固化現象

図4-12. 水中固化ダイレクトライティング

図4-13. ツイスト・コロイド構造体

PVB/エタノール系スラリーの水中固化現象では、スラリー中からのエタノールの移動(浸透圧)と水溶媒からの浸透圧の平衡によって、スラリー固化体の界面が形成される。このバランスを意図的に崩せば、界面は不安定になる。本実験ではこの不安定性により、自発的に多孔構造が形成されることを見出した。図4-14はこのようにして作製されたYSZの多孔構造体(焼結体)である。

図4-14. 界面不安定性によって形成された多孔構造体

## 4.5.2. パターン精度の検討

4.4で示したコロイドゲルを2次元平面上にダイレクトライティングし、得られたコロイド構造体のパターン幅を光学顕微鏡観察にて評価した(図4-15参照)。この観察の範囲内で、線幅変動の目標値を達成した。

図4-15. 2次元ダイレクトライティングのパターン

#### 4.5.3. スラリー組成の最適化

4.4節で示したコロイドゲルにおいて、添加するPVB濃度、並びに平均粒子表面間距離との関係を詳細に検討し、ダイレクトライティング可能なスラリー組成を求めた。

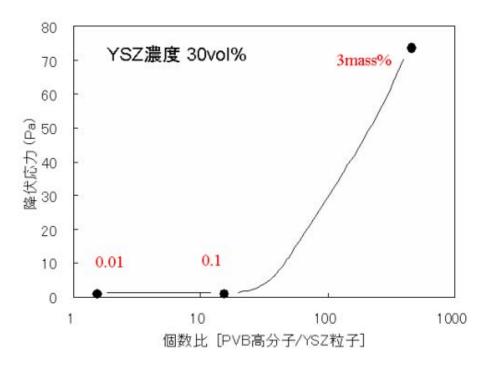

図4-16 PVBとYSZ粒子の個数比とスラリー降伏応力との関係

図4-16にスラリー中のPVB(高分子)とYSZ(ナノ粒子)の個数比とスラリーの降伏応力との関係を示す。スラリーの降伏応力とは、スラリーが弾性(固体)から粘性(液体)へ変化する際に必要な応力値のことであり、ゲル化指標の一つである。ダイレクトライティングには数十Pa以上の降伏応力が求められる。この実験ではスラリー中のYSZ濃度は30vol%であり、このときの平均粒子表面間距離は約7nmである。PVBのエタノール中のサイズは約15nmであることから、条件は満足する。なお、平均粒子表面間距離はコロイド分野でよく使用される次式より算出した。

$$di = d\left(\sqrt{\frac{1}{3\pi(\nu/100)} + \frac{5}{6}} - 1\right) \tag{1}$$

ここで、diは平均粒子表面間距離、dは分散粒子の粒子径(今の場合、YSZ)、vは濃度である。

同図からわかるように、ゲル化にはPVBと粒子個数比が極めて重要である。本実験の範囲内ではゲル化に要する個数比はPVB/YSZ>100、すなわち、PVBの数がYSZの数より2桁以上大きいこと

が必要である。

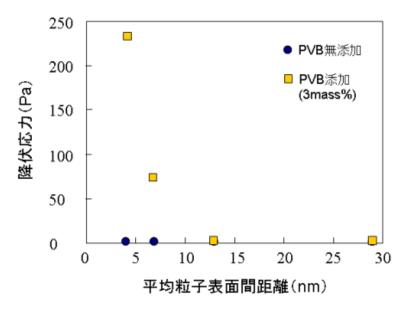

図4-17に平均粒子表面間距離とスラリー降伏応力との関係を示す。この実験ではスラリー濃度をパラメータにし、(1)より算出される平均粒子表面間距離を用いた。PVB添加量は3mass%であり、これはPVBの個数がYSZの個数より二桁大きい条件である。同図からわかるように、平均粒子表面間距離がPVBのサイズより小さい場合、好ましくはその半分のサイズ以下でゲル化が生じる。 PVB添加量はYSZ粒子に対し3mass%であり、4.2節で述べたように通常の熱処理条件で十分脱バインダー可能である。

図4-17. 平均粒子表面間距離とスラリー降伏応力との関係

#### 5. 膜状試料の高周波誘電特性の評価技術の開発

#### 5.1. 目的

アドバンスド LTCC 開発を目的として、MEMS 技術と LTCC 技術との融合に必要となる要素技術に関し、特に膜状試料の高周波誘電特性の評価技術を中心に開発する。具体的な実験内容を以下に示す。

#### ① ギガヘルツ帯誘電特性評価技術の開発

アドバンストLTCCの開発には、低誘電損失を有する膜状試料のギガヘルツ帯における 誘電特性の評価技術の開発が必須となる。試料表面にマイクロストリップ配線を形成し伝 送特性を評価する方法はあるが、ギガヘルツ帯での損失は配線の品質で大きく変化するた め、誘電体のみの評価には適さない。そこで、特性が既知の基板上に平面共振器を形成し、 誘電特性を評価する方法を開発する。

#### ② テラヘルツ帯誘電特性評価技術の開発

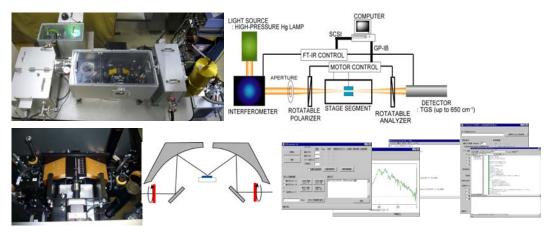

高周波用セラミックスの誘電物性はイオン分極により支配され、その特性を原子レベルで理解するには格子振動の生じている周波数領域(テラヘルツ帯)で誘電特性を評価することが必要となる。そこで、バルク試料および膜状試料について、これを可能とするテラヘルツ帯エリプソメータを開発する。

#### 5.2. 研究成果

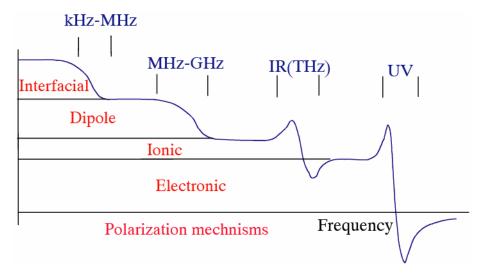

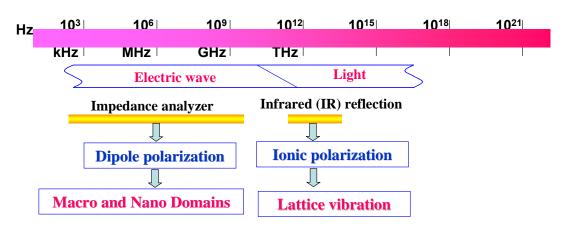

#### 5.2.1. 広帯域誘電スペクトルの測定方法の確立

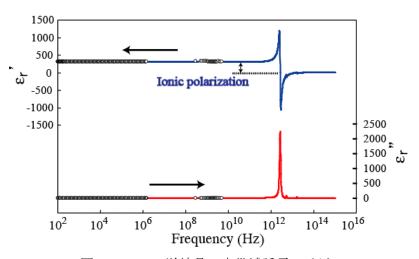

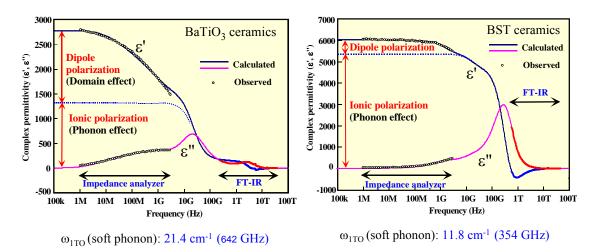

図 5-1 に示すように物質の分極機構には、電子分極(electric polarization)、イオン分極 (ionic polarization)、双極子分極(dipole polarization)、界面分極(interfacial polarization)の4種類がある。高周波 LTCC 用部材で重要となるのは、このうち主に双極子分極とイオン分極である。すなわち、GHz 帯から THz 帯にかけての誘電特性はこれら2つの分極応答で決まり、分極応答と材料組成、材料構造の関係を明らかにすることは、新規材料の開発に必要不可欠となる。電磁波は、図5-2に示すように THz 領域で電波と呼ばれる領域から光と呼ばれる領域へと変化する。これに伴い、誘電特性の評価法も電気的な評価法から光学的な測定法へも変化する。本事業では、kHz から THz にかけての超広帯域において誘電率の周波数依存性(誘電スペクトル)を測定することを目的としてシステムの開発を行った。以下に本事業で開発した GHz 帯域での誘電特性評価法と THz 帯域での誘電特性評価法について説明する。

図 5-1. 固体の分極機構と誘電緩和

図 5-2. 電磁波の周波数と誘電率の測定法

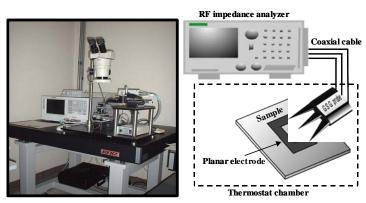

## (1) ギガヘルツ帯域での誘電特性の測定

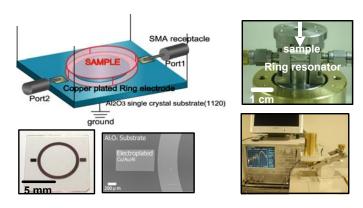

広帯域での誘電スペクトル測定において、kHzから MHz 領域にかけては、試料の上下面に電極を形成しキャパシタンスを測定することで容易に誘電率を求めることができる。しかしながら、GHz 領域になると、電磁波の波長が短くなるため、試料を R, C, L の等価回路で表す集中回路定数の近似が成立しなくなり、試料中での電磁波の位相の変化を考慮した分布定数回路を用いる必要がある。また、測定系の寄生インピーダンスの影響も無視できなくなるため、測定プローブからなるべく短距離で電磁波を給電する工夫が必要となる。本事業では、これらを考慮し、電磁界解析シミュレータを用いて設計した平面電極を試料表面に形成し、高周波インピーダンスアナライザで複素アドミタンスを測定し、測定結果を電磁界シミュレータを用いて解析することで、試料の誘電率を算出する方法を考案した。測定システムの概要を図 5・3 に示す。このシステムを用いることで、従来まで困難であった高誘電率材料の複素誘電率を 1・3GHz まで測定できるようになった。これ以上の周波数で

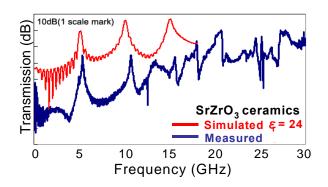

は共振回路を試料表面に形成し、その共振周波数と共振ピークの急峻性から誘電率と誘電損失を見積もる法を開発した。共振回路として、図 5-5 に示すように試料上にリング共振器を形成した。 $\mathbf{SrZrO_3}$ セラミックスについての測定例を図 5-6 に示す。電磁界シミュレーションにより得られた共振周波数付近に共振ピークが観測されていることがわかる。このリング共振器法により、低損失、低誘電率材料に関しては  $\mathbf{30GHz}$  程度までの測定が可能となった。

図 5-3. GHz 帯域での誘電率測定システム

図 5-4. リング共振器法による GHz 帯域での誘電率測定システム

図 5-5. リング共振器法による SrZrO3 セラミックスの測定例

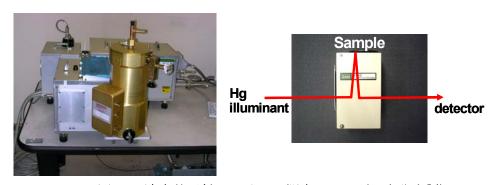

図 5-6. 遠赤外反射スペクトルの測定システム(日本分光製)

#### (2) テラヘルツ帯域での誘電特性の測定

テラヘルツ帯の測定では、電磁波は光波として取り扱わなければならないので、遠赤外領域で試料の反射スペクトルを測定し、これを解析することで試料の誘電率を求めた。測定システムの外観を図 4.2-6 に示す。反射率  $R(\omega)$ と複素誘電率  $\epsilon$ \* $(\omega)$ には以下の関係式がある。

$$R(\omega) = \left| \frac{\sqrt{\varepsilon^*(\omega)} - 1}{\sqrt{\varepsilon^*(\omega)} + 1} \right|^2$$

また、準量子論的理論によると、イオン分極による試料の誘電率と格子振動パラメータには、以下の関係がある。

$$\varepsilon *(\omega) = \varepsilon_{\infty 1} \prod_{j=1}^{n} \frac{\omega_{jLO}^{2} - \omega^{2} + i\gamma_{jLO}\omega}{\omega_{jTO}^{2} - \omega^{2} + i\gamma_{jTO}\omega}$$

ここで、 $\epsilon_{\infty 1}$ は電子分極による誘電率、 $\omega_{jLO}$ ,  $\omega_{jTO}$ は $\mathbf{j}$ 番目の縦波光学(LO)および横波 光学(TO)フォノンの周波数、 $\gamma$ はダンピング因子である。この式より、物質中の格子振動 パラメータがわかれば、複素誘電率が計算できることがわかる。本事業で開発した解析法 では、格子振動パラメータを変数として複素誘電率から反射率を計算し、反射率の実測値 と一致するように格子振動パラメータを非線形最小2乗法により精密化し、最終的に最も 確からしい複素誘電率を得るというものである。

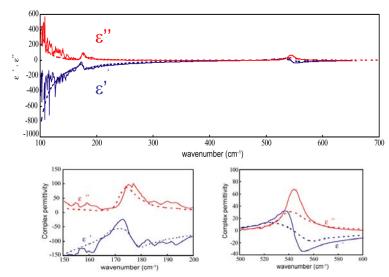

#### (3) ペロブスカイト型誘電体の広帯域誘電スペクトル

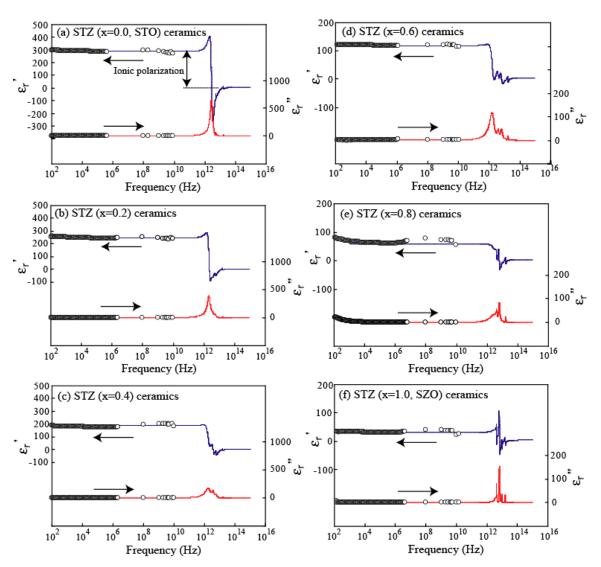

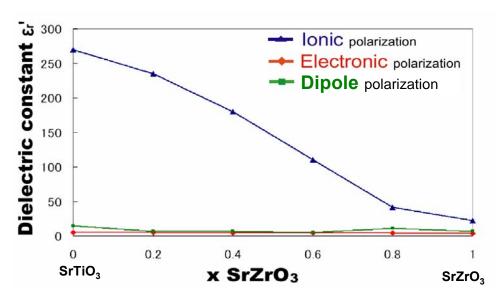

上に述べた測定システムおよび解析法を用いて得られた  $SrTiO_3$  単結晶の超広帯域誘電スペクトルを図  $5\cdot7$  に示す。本事業により初めて明らかとなった結果である。図中の白丸は GHz 帯域での測定法の結果である。リング共振器法により 30GHz 程度までの測定が可能となっている。THz 帯域の測定結果を解析することで、 $SrTiO_3$  の誘電率はほぼ 100% イオン分極により決まっていることが明らかとなった。ペロブスカイト構造を有する  $SrTiO_3$  の Ti イオンのを徐々に Zr イオンで置換固溶したときの誘電スペクトルの変化を図  $5\cdot8$  に示す。固溶体形成により、誘電率は徐々に低下し、共鳴吸収ピークの形状が不明瞭になっている。これは、同じイオン位置に Ti と Zr イオンが混在するために、全ての格子で同じ格子振動が起こらなくなるためである。Ti イオンを全て Zr イオンで置換固溶した  $SrZrO_3$  では共鳴吸収ピークは鋭くなっている。解析の結果、これら全ての試料の誘電率はイオン分極により支配されることが明らかとなった(図  $5\cdot9$ )。

図 5-7. SrTiO3 単結晶の広帯域誘電スペクトル

図 5-8. SrTiO3 (STZ x=0.0)と SrZrO3 (STZ x=1.0)の固溶体の広帯域誘電スペクトル

$SrTiO_3$ - $SrZrO_3$ 系固溶体では、図 5-9 に示したように誘電率の起源はイオン分極であるが、 さらに詳しく、どの振動モードが誘電率の発生に寄与しているかを解析した。立方晶系ペロブスカイト化合物には、Slaterモード、Lastモード、酸素 8 面体変位モードの 3 つの格子振動モードが存在する。

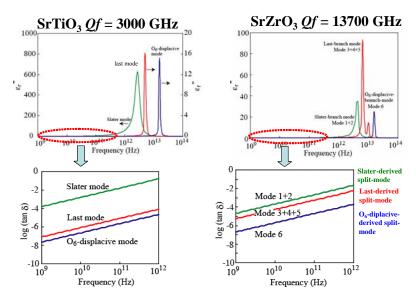

アドバンスト LTCC デバイスの多くは GHz 帯という高周波領域で使用される。誘電体材料への要求で最も重要なものは、高周波領域での損失の低さである。誘電損失は誘電正接  $(tan\delta\Box$ の逆数である Q 値により評価され、Q 値が高いほど低損失材料ということができる。 Q 値は、理論的に周波数 f に比例するため、材料の性能指標としては一般的に Q 値に周波数 f を乗じた Q 値が用いられる。これまでの経験則で、誘電率の高い試料は Q 値が低いことは知られていたが、その原因は不明であった。本事業で開発した測定・解析法を用いることで、この原因を特定することができた。 $SrTiO_3$  は比誘電率 290 で Q 値が 3000 GHz

であるのに対し、 $SrZrO_3$  は比誘電率が 30、Qf 値が 13,700 GHz である。Slater, Last,酸素 8 面体変位モードによる誘電損失の周波数依存性を図 5-10 に示す。 $SrZrO_3$ の Mode 1, 2, 3 はそれぞれ Slater, Last,酸素 8 面体変位モードに由来する格子振動モードに対応している。図から明らかなように、GHz 帯域での誘電損失は、THz 帯域にある各振動モード由来の誘電損失ピークの裾により決定される。GHz 帯域での誘電損失に対する各振動モードの裾の影響を下方の図に示した。 $SrTiO_3$  では Slater モードの裾の影響で誘電損失が大きくなっていることがわかる。 $SrTiO_3$  の高い誘電率は Slater モードの寄与であることは前に述べた。理論的に格子振動の光学横波モードの振動数が低く、縦波モードとの差が大きくなるほど、誘電率は高くなることが知られている。

図 5-9. SrTiO3 への Zr の置換固溶による各分極機構の寄与の変化

図 5-10. SrTiO3 および SrZrO3 の誘電損失の周波数依存性

すなわち、 $SrTiO_3$ では、Slater モードの周波数が低いために誘電率が高くなっている。このことは、Slater モードによる誘電損失のピークの裾が低周波領域まで影響を及ぼすことを意味している。この影響により、 $SrTiO_3$ の誘電損失は高くなり Qf 値は低下する。「誘電率が高い試料ほど Qf 値が低下する」という従来までの経験則は、この考え方で矛盾なく説明できることがわかる。

アドバンスト LTCC デバイスで使用される誘電体は、従来までの低誘電率、低損失な材料だけでなく、デバイスへ新規機能付加を目的として高誘電率材料も検討されようとしている。しかしながら、 $BaTiO_3$ や $(Ba, Sr)TiO_3$ の GHz から THz 帯にかけての誘電率はこれまで全く報告されていなかった。本事業で開発したシステムを用いて、これら材料についても広帯域誘電スペクトルを測定した。 $BaTiO_3$ ,(Ba,Sr) $TiO_3$ の広帯域誘電スペクトルを図5-11に示す。 $BaTiO_3$ の誘電率には双極子分極の寄与が多く含まれている。この双極子分極は強誘電体ドメイン壁の電場応答によるものである。 $BaTiO_3$  はドメインの寄与により高い誘電率を示すが、双極子分極の緩和周波数は GHz 帯にあるため、この周波数領域で誘電損失は大きくなる。一方、(Ba,Sr) $TiO_3$ の高い誘電率はほぼイオン分極により発生している。これにより、GHz 帯域での誘電損失は比較的低くなる。この結果より GHz 帯域で使用する誘電体としては、 $BaTiO_3$ よりも(Ba,Sr) $TiO_3$ が適していることがわかる。

以上のように、本事業で開発した測定システムを用いて誘電体の広帯域スペクトルを測定することで、物性発現の起源を知ることができる。従来までの試行錯誤的な材料開発手法には限界があり、偶然特性の良い材料を見つけたとしても、その材料をさらに改善したり、適切に使いこなすことはできない。物性発現の起源を見極めた上での材料・デバイス開発は、アドバンスト LTCC デバイスの実用化を諮る上で極めて極めて貴重であると考えている。

図 5-11. BaTiO3 および(Ba, Sr)TiO3 (BST)セラミックスの広帯域誘電スペクトル

#### (4) テラヘルツ帯域でのエリプソメータシステムの構築

これまで述べた測定・解析法で、誘電体の超広帯域誘電スペクトルの測定が可能となっ たが、THz 領域での誘電率の決定において、1点だけ、不確かな部分が残されている。こ れは、反射率という1つの物性量を解析することで複素誘電率(誘電率の複素成分)とい う2つの物理量を最小2乗法により求めている点である。すなわち、図5-11の結果は解の 1つではあるが唯一解(真実)であるか否かは正直なところ不明である。通常の光学測定 では反射率と透過率という2つの物理量を測定し、誘電率の複素成分を決定している。し かしながら、ペロブスカイト型誘電体はテラヘルツ領域で不透明なため透過率測定は不可 能である。そこで、本事業ではテラヘルツ帯域でのエリプソメータを開発することを試み た。エリプソメータは、平坦面を持つ試料に偏光を入射し、反射光の偏光状態を解析する ことで試料の複素誘電率を決定する装置で、反射光のみの情報から誘電率の複素成分を決 定できるという特徴を有する。テラヘルツ帯域でこの装置を使うことにより、薄膜試料、 不透明バルク試料についてもイオン分極の緩和周波数領域での誘電スペクトルを直接測定 することができる。図 5-12 に構築したシステムの構成を示す。このシステムはハード部分 だけでなく、制御・解析用ソフトウェアが非常に重要である。本事業では、ハードの一部 とソフトウェアの開発を行った。この装置を用いてSrTiO3単結晶について測定した結果を 図 5-13 に示す。実線は従来法の測定結果、点線はエリプソメータによる測定結果を示して 現時点では、精度はまだ十分ではないものの、解析に全く仮定を用いていないエ リプソメータの結果は従来法とほぼ一致していることがわかる。本システムは、今後の改 良によりバルク・薄膜試料を問わず直接的にテラヘルツ帯での誘電スペクトルを測定でき る唯一の方法として、アドバンスト LTCC 用材料の開発にとって非常に強力な手法となる と考えている。

図 5-12. テラヘルツ帯エリプソメータの概要

図 5-13. SrTiO3 単結晶のテラヘルツ帯域での誘電スペクトル (実線:従来法、点線:新規に開発したエリプソメータの測定結果)

# 6. MEMS デバイスの低温・低荷重ストレスフリー実装に向けたガスデポジション法による錐形バンプの作製

## 6.1. はじめに

電子機器の小型化・高機能化に伴い、半導体LSIデバイスについては高性能化、高集積化、高速化、低消費電力化にますます拍車がかかっている。一方、LSI デバイスの実装技術については、これまでワイヤーボンディング接続を用いて2次元に平面実装されてきたが、さらなる高集積、高速化を図るために、貫通電極(TSV: Through Silicon Via)とバンプを用いた3次元集積実装方式への移行が検討されるとともに、CMOS(Complementary Metal Oxide Semiconductor)デバイス、CCD(Charge Coupled Device)、メモリデバイスなどの半導体デバイスに加え、MEMS(Micro Electro Mechanical System)デバイスなどの多種多様な電子デバイスを含めた高密度複合実装方式への要求も高まってきている。さらに、従来のデバイスを個片チップでパッケージに実装するチップレベル実装方式に加えて、直接、デバイスが形成されたウェハ上にパッケージ構造を作り込むウェハ・レベル・パッケージ(WLP)方式によって究極の量産性が求められている。MEMS デバイスは、プレーナ型のLSIチップとは異なり、中空構造、高アスペクト比の立体構造で特有の3次元構造を有することから、その実装において要求されるのは、LSI デバイスの3次元実装における高密度化ではなく、むしろ、低温・低荷重のストレスフリー実装である。また、MEMS デバイスは LSI デバイスと比較して最終的に外部へ接続される電極パッドのサイズは大きいため、それに対してバンプサイズも必然的に大きくする必要がある。

本プロジェクトにおいて、我々は、3 次元実装における低温・低荷重のストレスフリー実装を目指して、ガスデポジション(GD)法による錐形バンプの作製を行ってきた。錐形バンプは先鋭形状であることから接続端子間のフィラーなどの樹脂を容易に排斥できること、そして、先端の強度が低いことからバンプの高さばらつきによる接続不良を低減できること、チップへの機械的ダメージを低減できることが挙げられ、さらに、バンプが圧縮変形した際には、水平方向への広がりが抑制されるため、狭ピッチ化が可能である、などの利点が多い(図 6-1)。

本稿では、まず GD 法を用いた錐形バンプの形成メカニズムについて触れ、プロセス上の問題 点を明らかにした上で、その問題点を克服する解決手法を説明した。 最終的に形成した錐形バンプについては、微小圧縮試験、フリップチップ接続試験を行い、錐形バンプの有用性を示すことができたので報告する。

<u>低温・低荷重のストレスフリー接続</u>のためには、従来のパンプ形状と比較して、圧倒的に<u>錐形パンプ</u>が優位

図 6-1. 錐形バンプの優位性

#### 6.2. 錐形バンプの形成メカニズム

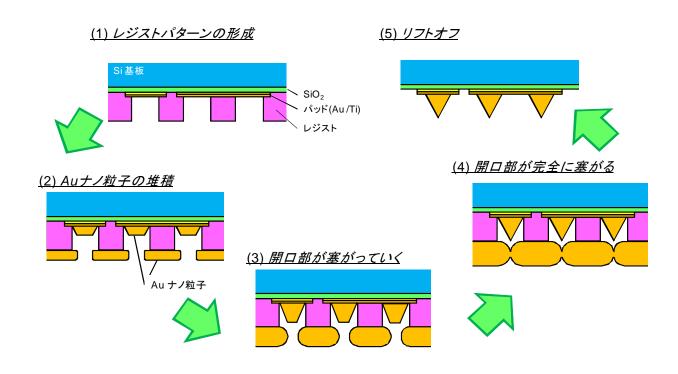

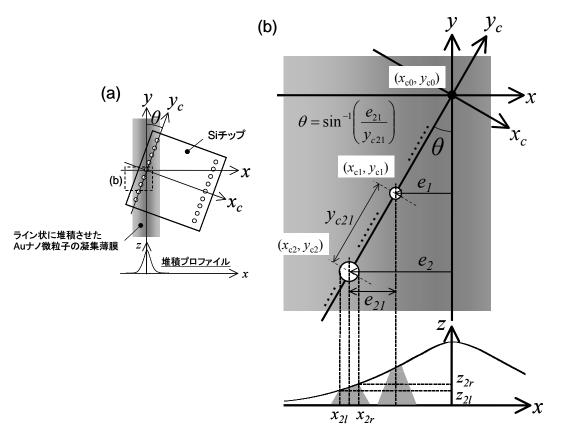

GD 法による錐形バンプ作製手法は、実にシンプルである。まずバンプのパターンとなるレジスト パターンをリソグラフィ技術により形成し、GD 法によりレジストパターン上に Au ナノ粒子を堆積させ ることによって、自己形成的に錐形バンプが作製されるプロセスである。図 6-2 に GD 法により Au ナノ粒子の凝集薄膜を堆積させる様子と錐形バンプが自己形成的に作製されるメカニズムを示す。 Au ナノ粒子を生成し、 基板上へその凝集薄膜の堆積を具現化する装置は、2つのチャンバーの ナノ粒子生成室と成膜室、とそれらを接続する搬送管とノズルで構成されている。ナノ粒子生成室 内の成膜材料である金属を導入したるつぼは、高周波誘導加熱コイルでその金属の融点以上に 加熱され、るつぼ内の金属は蒸発する。He ガスはナノ粒子生成室底面のるつぼ下方向から層流 状態となって導入され、るつぼ側面を通過し、るつぼ上方向に真空排気される。ナノ粒子生成室は この He ガスで 1 気圧程度に保たれ、He ガス雰囲気中で蒸発した金属原子は、He ガス分子と衝突 し、冷却され、ナノ粒子を形成する。成膜室はナノ粒子生成室より減圧されており、この圧力差によ り、るつぼ上方に生成されたナノ粒子は He ガスとともに搬送管に吸い込まれ、搬送管先端にあるノ ズルより吹き出される。成膜室に到達したナノ粒子は、基板表面に衝突し、ナノ粒子の凝集体とな って金属薄膜を形成する。ノズルから吹き出される He ガスはすぐに拡散するが、これに比べ十分 大きな質量を持つナノ粒子は、ノズル径の数倍程度の距離ではほとんど直進し、基板に堆積する。 このときステージを走査することによってライン状に金属膜を堆積したり、任意の箇所に金属膜を堆 積したりするなどが可能となる。

## 金属ナノ粒子を生成し、キャリアガスとともにノズルから基板へ吹き付けて成膜する手法

図 6-2. ガスデポジション(GD: Gas Deposition)法

このようにして、Si チップ上に形成されたレジストパターン上において Au ナノ粒子が堆積し、凝 集薄膜となる。このとき、単に真空蒸着やめっきなどの成膜手法であれば、ホールの形状と同じバ ンプが作製されるが、GD 法の場合、レジスト表面において、ナノ粒子が垂直方向に堆積するだけ でなく、水平方向にも拡散し堆積することから、図 6-3 にあるように、ホール上部にひさしを形成して しまう。これが功を奏して、ひさしが形成されたホール底面にはナノ粒子が堆積されず、ひさしの無 いホール底面のみに堆積されていく。このようにして、ホール底面にナノ粒子が堆積すると同時に ひさしも成長することから、徐々にバンプの形状はテーパー形状となっていく。最終的には、ひさし が完全にホールを塞ぐまでホールにナノ粒子が堆積するので、バンプの先端はおのずと錐形状に なる。完全にホールを塞いだ後は、ナノ粒子をいくら堆積させてもバンプ形状には寄与しないため、 全てのバンプが同一形状となる。GD 法によるナノ粒子の堆積が終了すれば、試料を有機溶剤に 浸漬し、レジストを溶解して、レジスト上部の金属薄膜を剥離するリフトオフ工程によって、錐形バン プが現れる。このようにして、リソグラフィによるレジストパターンの形成と GD 法によるナノ粒子の堆 積を組み合わせることによって、自己形成的に錐形バンプを作製できる。さらに、レジストパターン は、レジストの種類を変えたり、スピンコート時の回転数を変化させたりするなどして膜厚を数十 μm ~数百 nm まで容易に変化させることができるので、レジスト膜厚に応じたバリエーションの高いサ イズの錐形バンプが容易に作製可能となる。

<u>リソグラフィとGD法</u>を組み合わせることにより自己形成的に先鋭バンプを作製できる

図 6-3. GD 法による錐形バンプの形成メカニズムとプロセスフロー

# 6.3. これまでの問題点とアプローチ

GD 法において、金属の融点以上の温度に達したるつぼや300℃程度に加熱された搬送管を考慮すると、ナノ粒子を含んだHeガスの熱流体がレジストに熱ダメージを与え、レジストの熱変形によるバンプ形状の変化やレジストの基板への焼け付きによって有機溶剤で容易にレジストが剥離できない、などの問題が懸念されていた。特に MEMS デバイスの実装に必要なバンプのサイズは数十μmと大きく、これには数十μmのレジスト膜厚が必要なため、GD 法による熱流体から与えられる熱を放熱し難く、レジストに熱が蓄積されやすいことで、さらに熱ダメージを受けることが予想される。るつぼの温度をより高くし、Auナノ粒子の生成量を増加させ、Auナノ粒子を高速に堆積することによってバンプ形成の高速化を図れば、るつぼの温度上昇に伴ってさらにレジストへの熱ダメージ量が増えてしまう。GD 法の高速成膜に伴い上昇するレジストへの熱ダメージを軽減するために、新たにチップ取付治具とヒートシンクを設けた。実際に GD 法の成膜時において、基板温度を計測することで、レジストが有機溶剤によって容易に剥離可能なベーク温度以下であることを示し、厚膜レジストにおいても GD 法での錐形バンプ形成が可能となることを実証した。

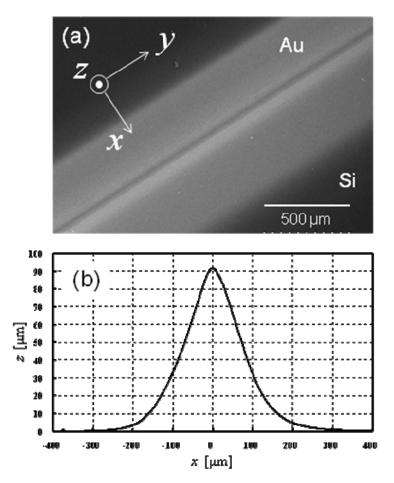

GD 法の成膜時には、ステージをスキャンすることによってライン状に Au ナノ粒子の凝集薄膜が 形成されるが、ノズル中心からスキャン方向に対して垂直に離れた点の成膜速度はノズル中心で の成膜速度と比較して遅く、バンプとなるレジストホールの位置がノズル中心から離れた点におい ては、ノズル中心でのバンプ形成時間と比較して、バンプ形成に多く時間がかかるという欠点があ る。このため、バンプ作製と同時に、直接 Si 基板上へ GD 法で Au ナノ粒子を堆積させ、この堆積 プロファイルを測定し、この堆積プロファイルを用いることで作製されたバンプについて、ホールとノ ズルの位置関係、形成時間などについて考察し、高速形成のための効率的なバンプ形成につい て解析した。

#### 6.4. 錐形バンプの作製

#### 6.4.1 作製プロセス

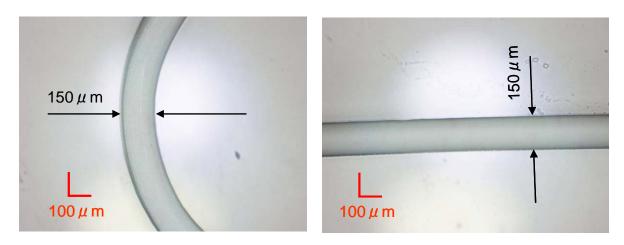

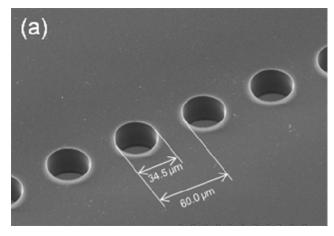

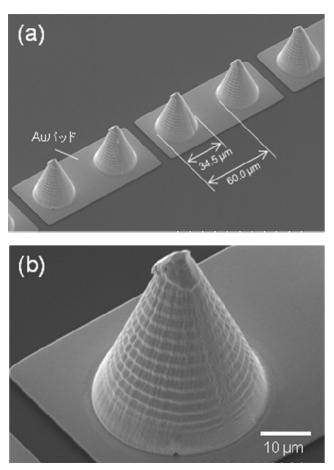

図 6-3 に示したプロセスフローに合わせて、リソグラフィによってバンプとなるレジストホールパターンを形成し、GD 法によって Au ナノ粒子をレジストホールパターン上に堆積するという一連の実験内容を述べる。バンプを形成するパッド間はスパッタ SiO<sub>2</sub> 膜(膜厚: 300 nm)で電気的に絶縁され、パッドはバンプとの密着性を考慮して Au(500 nm)/Ti(20 nm)を真空蒸着して形成した。レジストは汎用の厚膜レジスト AZP4903(AZ electric materials)を用い、パッド位置に合わせてパッド上部にバンプとなるホールパターンを、アラインメント露光を行うことによって形成した。レジスト膜厚は、スピンコートすることで 30.5 μm(触針式段差計 KLA-Tencor, alpha step IQ)の膜厚を得た。マスクでのバンプパターンは、サイズ φ30μm、ピッチ 60μm と設計したが、用いた露光機の焦点深度が 15μm 以下であるため、パッド表面が完全に露出するまで過剰に露光量を増やし、現像することで、最終的に、図 6-4 の SEM 写真に示すホール形状を得た。7.5 mm 角のチップにおいて、対向する 2 辺に、チップ端部から 500μm 離れた位置に 105 個のバンプとなるホールパターンを形成した。

図 6-4. レジストホールパターンの SEM 写真 (a)ホール列, (b)拡大図

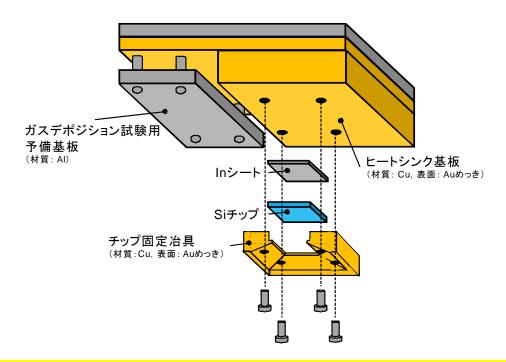

次に、このチップを図 6-5 に示すようにヒートシンクに取り付けた。ヒートシンクとして表面を Au めっき処理した Cu 板を取り付け、また、チップの 3 辺を、Au めっき処理した Cu 製冶具とそのヒートシンク材の間に挟み込み、さらにチップ裏面とヒートシンク材の間には、In シートを挿入して表面の密着性を向上させることによりレジスト表面の熱をより放熱しやすい設計にした。また、チップとは別の地点において事前に Au 堆積を確認する際、チップの温度上昇を防ぐために図のような予備基板を設けた。

基板の温度上昇を抑え、<u>厚膜レジストへの熱ダメージを軽減</u>して、レジストを剥離可能とするチップ取り付け

図 6-5 ヒートシンクの構造とチップの取り付け

チップを取り付けたこのヒートシンクをステージに設置し、ナノ粒子生成室、成膜室をそれぞれ  $2\times10^{-2}$ 、 0.3 Pa まで真空引きした。CCD カメラでノズル先端とチップ端部を観察しながら位置合せを行った後に、このレジストのホールパターン上に GD 法により Au ナノ粒子を堆積させた。この成膜条件としては、ノズル先端内径は  $\phi$ 500  $\mu$ m、ノズル-基板間距離は 4 mm であり、ナノ粒子生成室への He ガス供給流量を 30 L/min.以上とし、ナノ粒子生成室の He ガス圧力を 1 気圧に保った。この時、成膜室は 17 Pa であった。るつぼに Au(99.99%)を導入し、るつぼ温度は 1550  $^{\circ}$ C一定とし、ノズルは 300  $^{\circ}$ C程度に加熱した。ステージについては、スキャン速度を 2 mm/s、スキャン距離を 20 mm に設定し、連続して 100 回 (成膜時間: 16 分 40 秒) スキャンした。また、このチップに隣合せに配置した Si 基板にも同時に Au ナノ粒子を堆積させた。成膜中は、チップから 10 mm 離れた地点において K 型熱電対により基板温度を測定した。円錐バンプの作製プロセス条件を表 6.1-1 にまとめる。

成膜後は、チップを N-メチル-2-ピロリドンに浸漬し、超音波洗浄を行うことで、レジストおよび余分な Au 膜を剥離した。

表 6-1. GD 法の成膜条件

|                    | チップ                                      |

|--------------------|------------------------------------------|

| チップサイズ             | 7.5mm角                                   |

| 基板                 | Si(100) [スパッタSiO <sub>2</sub> (300 nm)付] |

| パッド材質              | Au(500 nm) / Ti (20 nm)                  |

| パッドサイズ             | 50 μm x 110 μm                           |

| レジスト               | AZP4903(Az electronic materials製)        |

| レジスト膜厚             | 30.5 μm *1                               |

| バンプのレジストパターン       | ∖34.5 μm *²<br>60 μmピッチ *²               |

| バンプのレジストパターン数 (/列) | 105個                                     |

| ガスデオ               | ペジション装置                                  |

| ノズル先端内径            | \500 μm                                  |

| ノズルー基板間距離          | 4 m m                                    |

| ナノ粒子生成室のHeガス圧力     | 100 kPa (~1気圧) [Heガス(99.99 %)]           |

| Heガス供給流量           | 30 L/min. 以上                             |

| 生成室の圧力             | 17 Pa                                    |

| るつぼ内成膜材料           | Au(99.99%)                               |

| るつぼ温度              | 1550℃                                    |

| ノズル温度              | 300℃                                     |

| 基板温度               | 63℃ 以下                                   |

| ステージスキャン速度         | 2 mm/s                                   |

| スキャン距離             | 20 m m                                   |

| スキャン数<br>(成膜時間)    | 100回<br>(16分40秒)                         |

<sup>\*1)</sup> 触針式段差計(KLA-Tencor, alpha step IQ)

#### 6.4.2. 作製結果

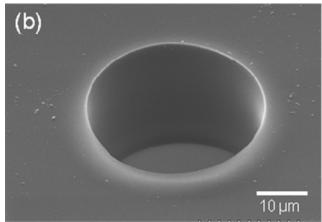

図 6-6 に作製した円錐 Au バンプの SEM(日立ハイテクノロジーズ, S-3500N)写真を示す。レジストパターンの形状に併せてバンプサイズ、ピッチともに一致している。この図 6-6(b)のバンプについてバンプ高さをレーザ顕微鏡(キーエンス, VK-9700)用いて測定すると、37.9 μm であった。これよりこの円錐バンプの傾斜角度は、65.5 度と分かる。レジスト膜厚は、30.5 μm であったため、バンプ先端は、このレジスト膜厚よりも 1.2 倍高く成長していることが分かる。この時、ひさしの形成速度は円錐バンプの堆積速度より 45.5%遅かったことを現している。例えば、50%の場合にバンプの傾斜角度が 63.4 度となり、バンプ底面の長さと高さが一致することになる。この SEM 写真を観察するとレジストの残留も無く有機溶剤で完全にレジストを剥離できている。GD 法での成膜中に測定した基板温度は、最大 63℃とレジストのベーク温度以下であったため、容易にレジストが剥離できたと

<sup>\*2)</sup> 電子顕微鏡(Hitachi, S-3500N)

考えられる。用いたヒートシンクの効果が十分に現れている。この基板温度は、一般的にめっき欲の温度と同程度であり、低温プロセスであることが言える。

図 6-6. 作製した円錐 Au バンプの SEM 写真 (a)バンプ列, (b)拡大図

## 6.4.3. 円錐バンプの形成時間についての考察

図 6-7 に円錐バンプ作製と同時に Si 基板に堆積させた Au ナノ粒子の凝集薄膜の高さ方向の形状プロファイルを示す。この形状プロファイルは、触針式段差計(KLA-Tencor, alpha step IQ)を用いて測定した。最大高さは 91.4 μm であり、この頂点から左右対称に非常に滑らかな形状となっている。この頂点がノズル中心位置に相当すると考えられる。もしノズル中心の延長上にホールの中心があった場合、100 回のスキャンで 91.4 μm の膜厚があることから、1 スキャンあたりの膜厚は、0.91 μm/scan となる。作製された円錐バンプの高さは、37.9 μm であるので、42 回のスキャンでこの円錐バンプが形成されたと考えられる。この実験条件では 10 秒で 1 スキャンする設定であるので、バンプ形成に要した時間は 7 分となる。すなわち 7 分で完全にホールが塞がり、後の 9 分 40 秒間の成膜は、バンプ形成には寄与しなかったことになる。この時、スキャン距離は 7.5 mm 角のチップサイズに対して 20 mm であったので、スキャン距離をチップサイズと同等に 7.5 mm にした場合には、20 mm のスキャン距離では 1 回のスキャン距離では 10 秒かかるのに対して 7.5 mm のスキャン距離では

3.75 秒に短縮されるので、円錐バンプの作製時間は 2 分 38 秒と換算される。この時、バンプ 1 個 はわずか 1.5 秒で形成可能となる。このように、 $30~\mu m$  厚の厚膜レジストにおいても GD 法での高速 成膜による熱ダメージをヒートシンク付加によって軽減し、 $30~\mu m$  サイズの円錐 Au バンプを作製できることを実証した。

図 6-7. ライン状に成膜した Au ナノ粒子の凝集薄膜の堆積プロファイル (a)SEM 写真, (b)堆積プロファイル

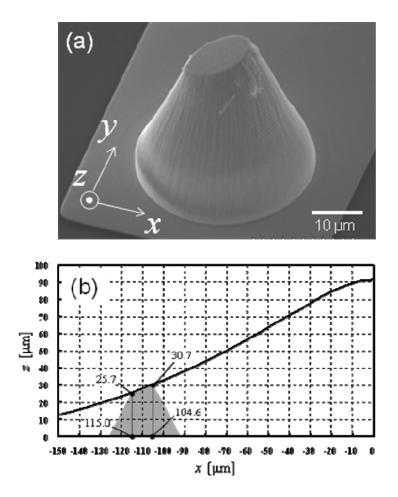

この円錐バンプ作製時間の算出例は、ホールに対してノズル中心位置が一致している場合であるが、実際には、チップの取り付けがスキャン方向に対して傾いていたり、CCDカメラでの位置合わせが十分でなかったりするので、ノズル中心とホールを高精度にアラインメントを行う機構を持たない現行の装置では、ノズル中心からホールが離れる場合が十分に懸念される。図 6-8(a)では、ノズル中心からホールの位置が離れており、この成膜条件では完全にホールを塞ぐことができずに途中で成膜が終了したことによって、円錐形状に形成し得なかったバンプの一例を示す。このバンプの上面の傾斜が右上がりであることから、図 6-8(b)の堆積プロファイル上において頂点より左側(x<0)の位置で作製されたバンプだと考えられる。このバンプの特徴点である上面の高さの最大値と

最小値をレーザ顕微鏡 (Keyence, VK-9700) で測定すると、それぞれ、30.7  $\mu$ m, 25.7  $\mu$ m であった。この値を堆積プロファイル上で x の値を読み取ると、それぞれ、104.6  $\mu$ m、115.0  $\mu$ m となる。この x の値の中間の値がバンプ中心の位置に相当すると考えられるので、このバンプの中心位置はノズル中心位置から 109.8  $\mu$ m 離れていたと推定され、このバンプ中心の高さは 28.2  $\mu$ m と堆積プロファイルから読み取れる。このバンプを堆積プロファイル上に重ねてみると図 6-8(b)のようになる。

図 6-8 ノズル中心からが 110μm 離れているホール位置において形成されたバンプ (a)SEM 写真, (b)堆積プロファイルにおけるバンプの位置

今回の実験では、ステージスキャン方向に対してチップの傾きは、図 6-9(a)のような位置関係にあると考えられる。図 6-9(b)のようにホール位置がノズル中心に近いほどホールは塞がり、ステージスキャン方向からホール列が角度  $\theta$  で傾いてチップが取り付けられていたと予想できる。このチップの取り付け傾き  $\theta$  を算出するために、前述のように、バンプの中心位置を堆積プロファイルより読み取り、5 個(300  $\mu$ m ピッチ) ずつ離れたバンプに対して図 6-9(b)に示すように傾き  $\theta$  を計算し、最終的に 10 回の平均値を算出すると、スキャン方向に対するチップの傾き  $\theta$  は 0.8 度となった。1 辺 105 個あるホールの 1 個目にノズル中心が一致していたとしても 1 個目のホールから 6240  $\mu$ m 離れた

105 個目のホールにおいてはノズル中心から 87 μm 離れることになり、この地点での膜厚はノズル中心での膜厚と比較すると 43.5 %も減少してしまう。

図 6-9. ノズル中心とホールの位置ずれ関係の模式図 (a)チップと堆積プロファイル, (b)堆積プロファイルに対するチップの傾斜角度の算出

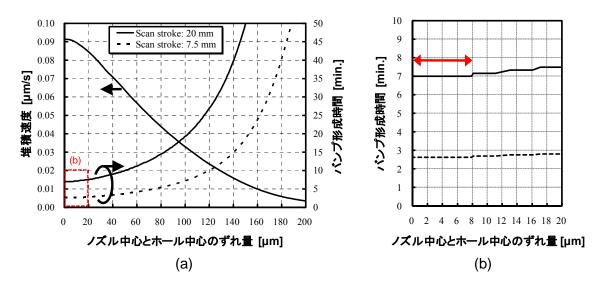

このように堆積プロファイルは、ノズル中心からホールまでの距離に対する成膜速度の変化として表わすことができる。図 6-10(a)に図 6-7(b)の堆積プロファイルの結果から求めたノズル中心から離れたホール位置に対する成膜速度の変化を示す。さらに、ノズル中心から離れたホール位置に対して今回の高さ 37.9 μm バンプの形成時間の変化を同図縦軸の第 2 軸に示す。ノズル中心からホールの位置が 140 μm 以上離れてしまうとバンプ形成時間は 40 分を要してしまう。そこで、スキャン距離をチップサイズと同じ 7.5mm と 37.5 %短くすれば、この分だけバンプ形成のためのスキャン回数を早くに達成できる。このようにバンプ形成を効率的に高速化するには、ホール位置をノズル中心と一致させる事と、ホールのある箇所のみに成膜するように必要最小限にスキャン距離を短くする事が重要である。バンプ 1 列全てが同一形状に形成される時をバンプ形成時間としているので、スキャン数は整数値にならなければいけないため、図 6-10(b)に示すように、ノズル中心位置から7.9 μm 離れたホール位置まではスキャン回数が 42 回と同じになる。この点のバンプ形成時間はノズル中心位置と変わらず形成できる。すなわち、光学的なアラインメント機構を付加し、比較的粗

い数 μm レベルのアラインメント精度を確保することができれば効率的かつ高速にバンプを形成できると考えられる。

図 6-10. ノズル中心とホールの位置ずれ量に対する成膜速度とバンプ形成時間の変化 (ステージスキャン速度: 2 mm/s)

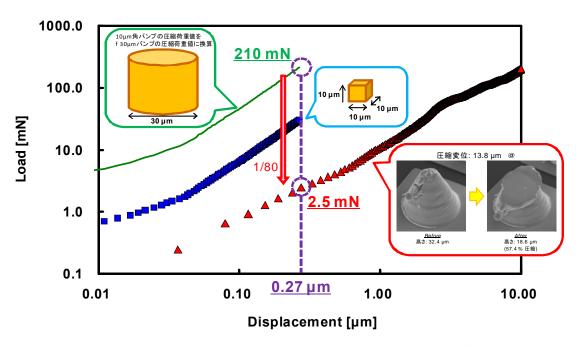

# 6.5. 微小圧縮試験

作製した  $\phi$  33  $\mu$  m、高さ 32.4  $\mu$  m の円錐バンプに対して、微小圧縮試験器 (島津製作所,MCT-W500、ダイヤモンド製平面圧子: $\phi$  50  $\mu$  m)を用いて微小圧縮試験を行って取得した荷重一変位線図を図 6-11 に示す。チップの温度は室温とし、平面圧子の負荷速度は等速7.75mN/s で一定として、円錐バンプに荷重を加えた。最大 300mN に達するまで圧縮変形させ、その時の平面圧子の変位量は 13.6  $\mu$  m であった。圧縮変形後のバンプ高さは 18.6  $\mu$  m となり、圧縮変形前との高さ比にして 57.4%圧縮したことになる。同図には、比較対象としてめっきによって作製した  $10\,\mu$  m 立方体のバンプについて微小圧縮試験を行った結果も併せて示している。めっきによって作製した  $10\,\mu$  m 立方体バンプの微小圧縮試験の結果を面積比で  $\phi$  30  $\mu$  m の円柱バンプに換算すると変位に対する荷重値は 7.1 倍となる。この  $\phi$  30  $\mu$  m に換算した円柱バンプと GD 法によって作製した錐形バンプを比較すると圧縮変位  $0.27\,\mu$  m において約 1/80 に荷重を低減できることが分かった。最終的に円錐バンプの高さは  $18.6\,\mu$  m まで圧縮変形されているが、円錐バンプ底面のサイズよりはみ出していないことから、狭ピッチでも隣同士のバンプが短絡する危険性が少ないことを示している。

図 6-11. 微小圧縮試験より得られた円錐バンプの荷重-変位線図

# 6.6. フリップチップ接続

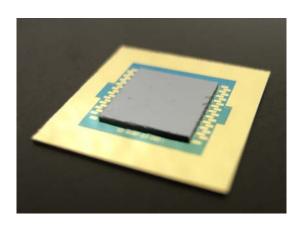

フリップチップボンダー(ピーエムティー製, CA300)を用いて、7.5mm 角の円錐バンプ付 Si チップを 15mm 角の Si 基板にフリップチップ接続した。下側の Si 基板には、上側のチップの円錐バンプに合わせて Au(膜厚:500 nm)の電極パッドが形成されている。フリップチップ接続の前に、円錐バンプや電極パッド表面に付着している有機物などの汚染を取り除くために両チップを  $O_2$ プラズマに 3 分間暴露した。フリップチップ接続時のチップマウンタヘッドの設定温度と荷重については、初期値を温度 36  $^{\circ}$  、荷重 10 Nとし、等速度で 5 秒間に温度 325  $^{\circ}$  、荷重 28 N まで上昇させ、その後 30 秒間、その設定温度、荷重値を一定に保つ条件でフリップチップを行った。フリップチップ接続した後の外観写真を図 6-12 に示す。

図 6-12. 円錐バンプを用いてフリップチップ接続したチップ外観

# 6.7. まとめ

LSI デバイスと MEMS デバイスの高密度複合実装において、低温・低荷重のストレススリー実装が要求されている。本プロジェクトにおいて、我々はこれまで、リソグラフィを用いてレジストによるホールパターンの形成技術と、GD 法を用いて Au ナノ粒子の堆積技術を組み合せることによって、自己形成的に先鋭バンプを作製してきた。GD 法での成膜過程において、基板温度はレジストのベーク温度以下であり、厚膜レジストでも熱の影響を低減させ、容易にレジストを剥離可能とすることで、低温プロセスにて MEMS デバイスに適用可能な φ30 μm サイズの円錐 Au バンプを形成することに成功した。さらに、ライン状に成膜された Au ナノ粒子の凝集薄膜の堆積プロファイルをバンプ形成と同時に取得することで、ノズル中心とホールの位置自然による堆積速度やバンプ形成時間の変化を定量的に評価し、ノズル中心とホールの位置合わせ精度が数 μm レベルのアラインメント精度においても高速に円錐 Au バンプを形成可能であることを示した。作製した円錐バンプは、従来のめっきで作製される柱状バンプよりも約 1/80 の低い荷重で圧縮変形し、低荷重のフリップチップ接合を可能とした。これらの結果より、この錐形バンプを用いた MEMS デバイスのストレスフリー実装の優位性を十分に示すことができた。

# 7. MEMS デバイスの低温・高密度・ストレスフリー実装に向けた無電解めっき 法による新微細接続法

#### 7.1. 本技術の背景

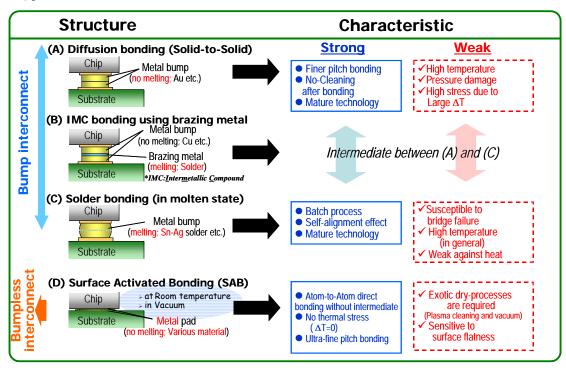

超高機能・高集積 MEMS デバイスの実現のためには、単機能の MEMS デバイス同士を組み合せる技術や、MEMS デバイスと半導体デバイスを組み合わせて、多機能化・高集積化する方法が重要となる。 MEMS デバイスと高機能 LSI デバイスを共存させた構造体(パッケージ、インターポーザなど) での多ピン接続では、フリップチップ (Flip-chip) 接続法が用いられる可能性が高いが、MEMS デバイスとの共存により、通常の Flip-chip 接続で要求される超高密度・高精度な接続以外に、デバイス保護の点から低温でかつ低加圧の接続が強く求められる。図 7-1 に示すように、現在、金属同士の接合による低抵抗接続が可能な Flip-chip 接続には、様々な方式があるが、熱ストレス、狭ピッチ対応、プロセス難易度などの観点から、それぞれの方式において固有の長所と短所が見られる。これより、現状のメタラジカル接続に属する Flip-chip 接続技術では、熱ストレス的に問題のない低温微細接続を実現するためには、高真空下での接合など、特殊な環境が要求されることがわかる。

図 7-1. 金属-金属接合メカニズムによる主な Flip-chip 接続方式とその特徴

常温接続法(SAB)を除き、これまでの微細接続を目的とした低温接続法は、金属バンプを接合界面で機械的に変形させる、もしくは、接合部を溶融させて、相手側の接合界面との接合を容易にする方法である。しかしながら、荷重による機械的変形を伴う接続方法では、今後のさらなる微細化に伴い、個々の微細バンプの変形を左右する、上下電極の位置合せ精度問題あるいは個々のバンプの荷重の制御が難しくなる可能性が高い。また、表面張力による位置修正(セルフアライ

メント)機構により、位置ずれに対しては比較的トレランスを有する溶融接続法では、微細化すればするほど顕著になるショート不良問題がネックとなる。一方、低温接続技術として著名な SAB 法に関しては、変形・溶融を必要としない一方で、原子レベルでの結合を進行させるため、対向するそれぞれの面の電極群の面内平坦度(コープラナリティ)が重要となるため、LSIチップ面積の増大に伴い、接続歩留りを維持することが難しくなることが予想される。

将来に向けたバンプ微細化に伴う Flip-chip 接続問題を克服する一つの解決策としては、接続における高温下、荷重印加などの機械的要因をできるだけ排除することが重要であり、「常温に近い低温」で、「機械的変形を伴わない」接続手法が有効であると見られる。機械的変形を与えずに接続を達成する最も単純な方法は、「バンプ形成」と「接続部形成」の両方のプロセスを同時に行なうことである。そこで、化学的反応、特に無電解めっきによる金属の析出反応を利用する方法に着目した。今回、機械的荷重を伴わない新しい低温接続法として「無電解めっきにおける導体間ブリッジ現象(異常析出)を応用した Flip-chip 接続法」を考案し[1]、いくつかの基礎的な評価を行なった。

#### 7.2 基本コンセプト

めっきを利用した電極接続法に関しては、特許、あるいは研究論文等でいくつか報告例[2-4]があり、それ自体は全く新しいコンセプトというわけではない。しかしながら、従来の方法の多くは、向かい合う電極表面でめっき膜を等方的に成長させ先端を接触させるタイプのものであり、狭ピッチ化が難しい、あるいは接合後の界面に微小な隙間が残留するなどの難点が有った。

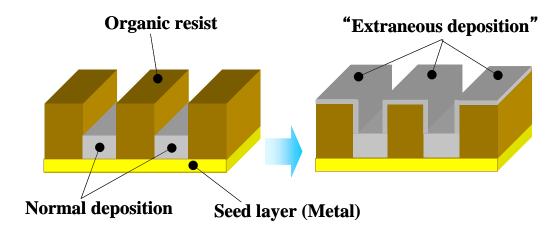

そこで本研究では、まず、離れた電極間にめっきで連続膜を形成することを考えた。微細ピッチを想定した場合、引き出し線等が不要な「無電解めっき」が当然第一候補となるが、ここで「離れた電極の間に、無電解めっきの金属析出に必要なシード層をどうやって形成するか?」ということが問題になる。この難題に対しては、無電解めっきで離れた導体パターン間に(シード層無しで)発生する"ブリッジ"という現象がひとつのヒントとなった。ここで"ブリッジ"とは、図 7-2 に示すように本来は析出しないはずのレジスト等導体以外の絶縁物表面(非活性面)に発生する金属析出のことである。ブリッジは、一般に"異常析出"と呼ばれるめっき不良のひとつであり、これを抑制する様々な対策が講じられている。しかしながら、ブリッジによる析出膜は、電極間に形成された連続膜の一種であり、これをコントロールできれば、電極間接続に応用できるポテンシャルを有するはずである。そこで、無電解めっきによるマイクロパターニングにおいて特にブリッジを発生しやすい[5-8]とされる、ジメチルアミンボラン(DMAB)を還元剤とする無電解ニッケルボロン(Ni-B)めっき浴を用い、離れた電極間の電気的接続行なう検討を行なった。

図 7-2 めっきにおいて発生する異常析出(ブリッジ)現象

今回用いる無電解 Ni-B めっきは、電子工業分野における(広義の)無電解ニッケルめっき全体の中では極めて少数派に属するものである。無電解 Ni-B めっきは主流のニッケルリン(Ni-P)めっきと比較して、めっき浴の安定性及びパターン選択性に劣るという短所がある一方で、めっきが低温(50~70℃)で行なえること、弱酸性~弱アルカリ性の(マイルドな)環境下でめっきが可能なこと、はんだ付け性・ボンディング性に優れ(B含有率1%以下)こと、硬さ・耐摩耗性に優れる(B含有率3~6%)こと、等々の特徴から、主に特殊な用途の自動車用部品、電子部品などに用いられている。

無電解 Ni-B を用いた今回の接続法の主な構成要素をまとめると下記となる。

- (a)ある間隔をおいて存在する対向電極

- (b)めっきのベース材として対向電極間を橋渡しする絶縁樹脂

- (c)DMAB を還元剤とする無電解 Ni-B めっき浴

- (d)ブリッジが起こりやすいめっき条件(前処理,温度,pH等)

なお、ここで得られる Ni-B 析出膜は、バルクめっきのためのシード層としての役割を想定しており、最終的にはこの後 Au、Cu などのめっき膜を形成し接続を完成する。これ以降、対向電極間にブリッジを形成する方向にめっき膜が析出する現象を架橋前の段階も含め、「ブリッジ析出」と呼ぶことにする。

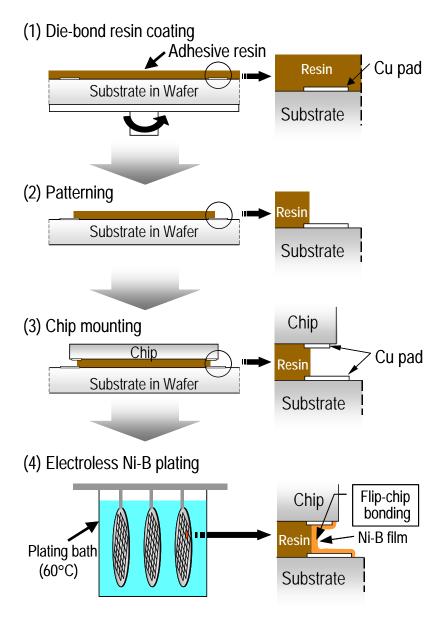

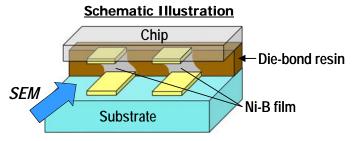

#### 7.3. 無電解めっき法による接続プロセス

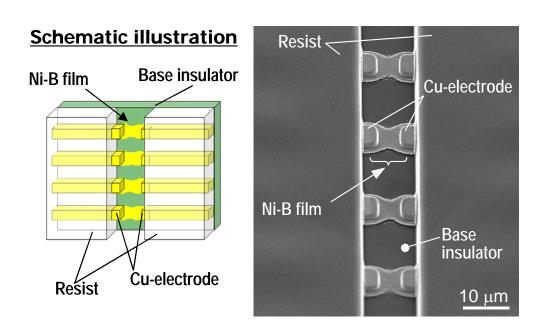

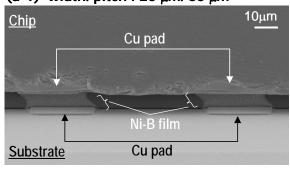

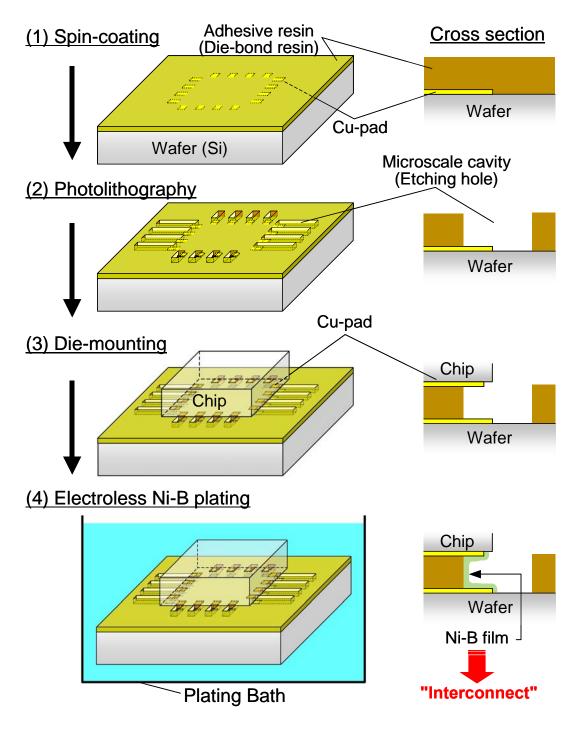

本手法をFlip-chip 接続に適用した場合のプロセス概要を図 7-3 に示す。最初に半導体チップを搭載する基板として用いるシリコン(Si)Wafer 上に均一な接着樹脂層を塗布し(1)、フォトリソグラフィ技術等によりチップ側と Wafer 基板側の対向する金属電極面の一部が露出するようにダイボンド・パターンを形成する(2)。次に Wafer 基板にチップをマウントする(3)。最後に無電解 Ni-B 浴(浴温:60  $^{\circ}$ C)に Wafer を浸漬し、ブリッジ現象により上下の対向電極間に Ni-B 膜を析出させる(4)。

Ni-B 膜は電極間の接着層の側壁表面に沿う形で析出し、継ぎ目のない金属接続が完成する。 このあとさらに本 Ni-B 膜をシード層とするバルクめっきを行い、最終接続形態となる。

図 7-3 無電解 Ni-B めっきを用いた Flip-chip プロセス概要

# 7.4. 新接続法の特徴

本研究における新接続法は、無電解めっきという化学的析出現象を用いたことにより、従来の Flip-chip 接続法と比較して下記のような特徴がある。

- a. 大気中での低温(~60°C)での金属間接続

- b. バンプ形成が不要なバンプレス接続

- c. 接続部を溶融させない非溶融型接続

- d. ダメージの少ない無加圧条件での接続

- e. Wafer レベルでの一括 Flip-chip 接続

a は、材料間の熱膨張係数の差に起因する熱応力を低減するものであり、b は、バンプ形成と接続を同時に行ないプロセス簡略化に寄与するだけでなく、微細接続部界面に接合欠陥の無い均質な接続構造を実現するものである。また、c は、溶融させないことで近接バンプとの干渉のない狭ピッチ接続を実現するものである。

#### 7.5 平面配置対向電極による接続性評価法

# 7.5.1 評価用テストチップ(TEG)の概要と作製プロセス

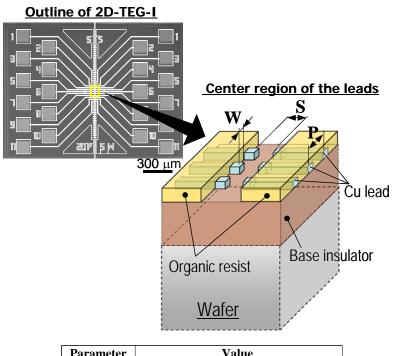

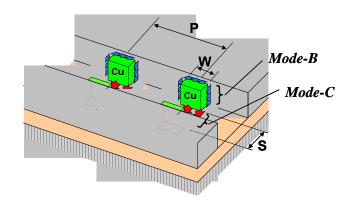

本手法による接続挙動をより正確に捉えるためには、接続前の電極周りの状態(ダイボンド樹脂厚、上下電極の対向関係など)をできるだけ一定にする必要がある。Flip-chip 実装を用いた場合のプロセス起因による寸法ばらつきの影響を排除するため、電極周りの寸法制御が容易な、「対向電極を平面内に配置した」テストチップ(以下 TEG; Test Element Group)(図 7-4)を用い、接続評価試験を行なった。以下、対向電極が二次元平面内に配置されている構造の TEG を総称して「2D-TEG」(two dimensional-test element group)呼ぶ。

Parameter

Value

S

(a) 5 μm

(b) 10 μm

W

(a) 5 μm

(b) 10 μm

P

(a) 10 μm

(b) 15 μm

(c) 20 μm

(d) 25 μm

(e) 30 μm

(f) 50 μm

図 7-4 対向電極を平面内に配置した TEG (2D-TEG-I)

まず最初に2D-TEG-Iでは、図7-3に示したプロセスと同様に、ブリッジ析出のベースとなる絶縁

樹脂(厚さ  $10 \, \mu m$ 、エポキシ系永久レジスト: 東京応化製 TMMR S2000)を 3 インチ  $\phi$ Wafer 上に塗布した。同樹脂は、リフトオフ (パターニング) 工程における有機溶媒 (アルコール等) 耐性,及びPhotolithography 工程におけるアルカリ (レジスト現像液) 耐性,の2つの観点から選定した。同Wafer 上に、図 7-4 に示すように、先端幅  $5\sim20\,\mu m$ 、ピッチ  $10\sim50\,\mu m$ 、先端の対向電極間距離  $5\,\mu m/10\,\mu m$  の銅(Cu)配線パターンを作製、対向部先端のみ金属表面が露出するようにめっき用レジスト(金バンプ形成用ノボラック系ポジ型レジスト: 東京応化製 PMER P-LA900PM)を塗布した。同レジストに関しては、無電解めっき時のアルカリ耐性,及びダイボンド樹脂(接着層)としての流用を考慮して選定した。ここで、本 TEG の構造(図 7-4)は実際の Flip-chip 接続を 90 度回転させて模擬した構造であり、電極先端がチップ/基板 各々の表面同士の対向電極、また絶縁樹脂表面がダイボンド樹脂側面にそれぞれ対応する。

# 7.5.2 2D-TEG による接続基礎実験-評価方法

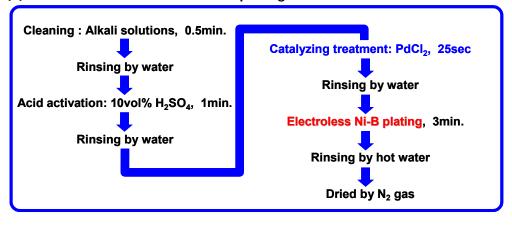

接続実験に用いた無電解 Ni-B めっきに関するめっき浴組成, プロセスフローを図 7-5 に示す。ここで、めっき浴への浸漬時間に関しては、予備実験により活性化金属面以外の樹脂表面へのブリッジ析出が同一試料で安定して確認された結果を受け、3 分とした。なお 3 分以下のめっき時間では同一デザインの試料でもブリッジ析出量にばらつきが確認された。

#### (A) Bath composition and operating conditions for electroless Ni-B plating

| Bath composition                                                                 |                                                                                    | Operating condition                                   |                                        |

|----------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-------------------------------------------------------|----------------------------------------|

| Dimethylamineborane (DMAB)<br>NiSO <sub>4</sub> -6H <sub>2</sub> O<br>Na-citrate | 0.025 mol dm <sup>-3</sup><br>0.1 mol dm <sup>-3</sup><br>0.1 mol dm <sup>-3</sup> | pH<br>Bath temperature<br>Agitation<br>Immersion time | 8.0<br>60 °C<br>No agitation<br>3 min. |

#### (B) Process flow of electroless Ni-B plating

図 7-5 無電解 Ni-B めっきにおける浴条件とプロセスフロー

図 7-5 に示しためっき浴に3分間浸漬し、対向電極間にNi-B 膜を析出させた後、金属顕微鏡を用いて対向電極間にブリッジ析出した Ni-B 膜を観察し、マクロな外観レベルでの接続状態の有無

をチェックした。外観観察で良好な電極間接続膜が確認された各電極に対して、導通試験を行ない、電気的な導通の有無をチェックした。Ni-B 膜の析出状態をさらに詳しく観察するため、形成された Ni-B 膜の SEM(走査型電子顕微鏡)観察を行なった。

一方、Ni-B 膜の組成・構造を調べるため、上記と同じ条件で Si ウエハ基板上に Ni-B 膜(ベタ膜)を形成し、ICP-AES (ICP 発光分光分析)法による組成分析、XRD(X 線回折)法による構造解析を行なった。

#### 7.5.3 接続膜の基本構造分析

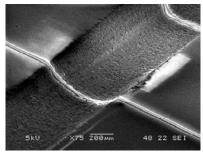

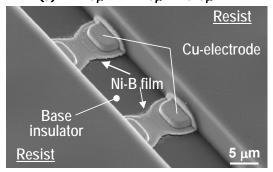

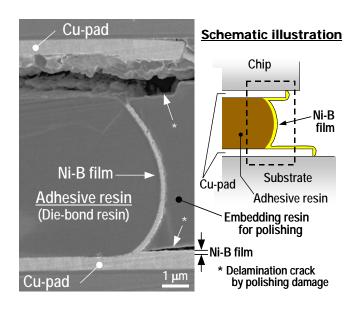

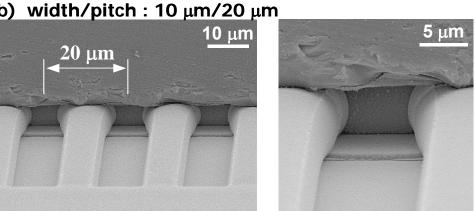

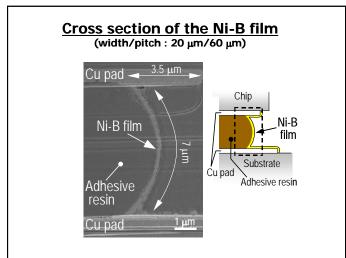

無電解 Ni-B めっき浴に 3 分間浸漬し、対向電極間に Ni-B 膜を析出させた後の接続部の代表的な SEM 観察像を図 7-6 に示す。

図 7-6 2D-TEG-I における SEM 観察像(幅:5μm-ピッチ:20μm-間隔:5μm)

図 7-6 は、幅 5μmーピッチ 20μmー電極間距離 5μm のパターンで得られた SEM 観察像である。 電極間にある中央部がややくびれた"砂時計"形状の薄膜がブリッジ析出により絶縁膜上に析出した Ni-B 膜である。離れた対向電極方向への選択的指向性(成長方向の選択性)を有しながら、接合界面に継ぎ目の無い金属膜が形成されていることがわかる。この砂時計形状は、対向電極の双方から析出膜が成長して行き、中央付近で両者の先端が重なり架橋された接続過程を示唆する。

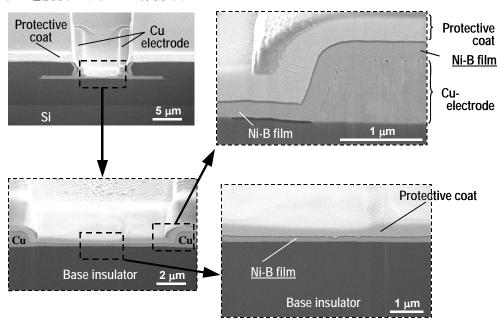

さらに接続膜の断面構造を調べるため、対向する Cu 電極と Ni-B 接続膜の中央を通る線に沿って切断した。得られた断面 SEM 観察像 (45 度上方からの観察像)を図 7-7 に示す。

図 7-7 において、最上層に白く見える薄膜層は FIB 加工用の保護膜であり、その下の層が Ni-B 析出膜である。本 SEM 観察像から、対向電極間のベース絶縁樹脂上に(シード層無しで) Ni-B 析出膜が形成されていることが観察できる。 Ni-B による接続膜は、露出している Cu 電極表面全体と

電極間のベース樹脂層をほぼ均一な厚さ(約 0.2 μm)で覆うように形成されており、中央部に継ぎ目(接続界面)が見られない連続膜が形成されているといえる。中央部に接続界面が見られないということは、「対向電極表面からスタートした析出膜が、0.2μの厚さを維持した状態で電極に向かって水平方向に成長し、先端部が出会う形で架橋される」という単純なプロセスでは無い可能性を示唆しており、それとは異なるプロセスで架橋が行なわれた可能性が高い。例えば、「最初に厚さを確認できないレベルの薄膜状態での接続を完成させた後、膜厚方向に成長した」可能性が考えられ、析出挙動の一端を示唆するものとして興味深い。導通試験の結果、光学顕微鏡(数百倍)レベルで Ni-B による接続膜が確認された部位においては、電気的導通も確認され、電気接続としても問題のない連続膜であることが確認された

\* All SEM images show the side views from a 45-degree angle against the cross-section surface

図 7-7 2D-TEG-I における接続部の断面 SEM 観察像

同一のめっき条件で得られた Ni-B 析出膜の分析結果を表 3.2 に示す。ICP-AES による組成分 析の結果、Ni-B 膜の組成は Ni 97 wt% - B 3 wt%であった。一般に DMAB を還元剤とする無電解 Ni-B めっき膜では、B 含有量が 0.2~1 wt%の低ホウ素タイプが多いため、本析出膜はこれと比較して高ホウ素タイプのものである。Ni-B の析出組成は、DMAB 濃度や錯化剤の種類などによって変化する[6]ため、本結果は、図 7-5 のめっき浴条件下で形成された析出膜の物性値であるといえる。

表 7-1 Ni-B 析出膜の組成/結晶構造/電気抵抗

| Analysis            | Results                                 | Remarks                                 |

|---------------------|-----------------------------------------|-----------------------------------------|

| Composition         | Ni 97 wt % — B 3 wt %                   | ICP-AES                                 |

| Crystal structure   | fcc Ni + amorphous* Ni-B                | XRD                                     |

| Electric resistance | 2 Ω<br>(Line width:30μm / Length:7.5μm) | 4-terminal<br>resistance<br>measurement |

\* Deduced from the XRD chart

XRDによる構造解析から、X線回折ピークは析出膜は面心立方(fcc)構造のNi以外には大きなピークは見られず、主にアモルファス構造のNi-Bからなるものと推定された。Ni-B合金は、B含有量が2wt%以下では結晶性の高い被膜が得られるが約3wt%以上になると非晶質になる[9]とされており、XRDの結果は上記ICP-AESの組成分析結果とも符合するといえる。

電気的特性に関しては、四端子測定の結果、幅  $30\mu m$  一電極間距離  $10\mu m$  のパターンで約  $2\Omega$  という値が得られた。この値は Ni-B の抵抗率 ( $\sim 100 \ [\mu \Omega \ cm]$ ) から予測される抵抗値とほぼ一致し、電極間に電気的に安定な連続膜が形成されていることがいえる。 Ni-B 析出膜の抵抗値は、 Cu の 60 倍以上、無電解 Ni-P めっき膜の約 2 倍という大きな値であるが、 Ni-B 析出膜は基本的にシード層の位置づけであり、最終形態ではこの上層にバルクめっき層が形成されることを想定しており、抵抗値の大小に関しては特に議論しない。

#### 7.5.4 電極間の空間的配置と接続挙動

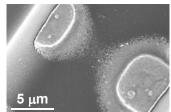

図 7-8 は、2D-TEG で得られた Ni-B 膜の代表的な析出例である。

(a) W:7.5 $\mu$ m-P:20 $\mu$ m-S:5 $\mu$ m

(b) W:5μm-P:25μm-S:10μm

(c) W:5μm-P:10μm-S:5μm

図 7-8 異なるデザインの対向電極における代表的なブリッジ析出例

図(a)が Ni-B 析出量が接続上適切な接続例で、これに対し図(b)は析出量が足りず未接続の例、一方図(c)は析出量が過剰で横の電極とのショート不良が発生している例を示す。、図(a)~(c)を比較すれば分かるように、析出量の大小、あるいはそれを左右していると見られる近傍の Cu 電極との空間的位置関係に呼応して、析出部の末端形状を変化させていることが観察できる。析出の方向は、無電解めっき時のサンプルの浸漬方向に依存しないことが確認されており、本析出が Cu 電極の存在方向に指向性のある選択的な析出現象であることがわかる。この特異的な析出現象は、一部のみが対向するようにオフセットさせた電極間の接続時に一層顕在化する。

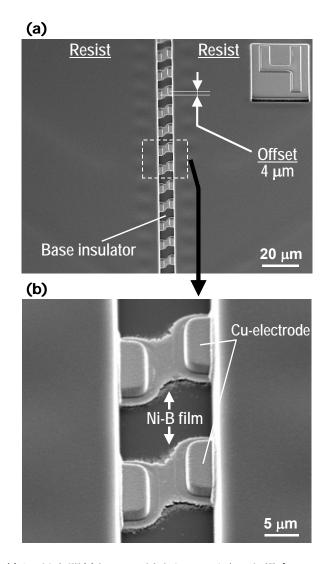

図 7-9 は電極の並ぶ横方向に  $4\mu m$  だけオフセットを与えたデザインの TEG における Ni-B 析出 後の接続例である。

図 7-9 電極の対向関係を 4μm だけオフセットさせた場合の Ni-B 析出膜 (W:7.5μm-P:20μm-S:5μm)

析出膜は位置ずれ方向に歪んだ砂時計形状を形成しており、対向電極方向に選択的指向性を有する析出挙動を示していることがわかる。つまり、電極間の位置ずれに追従するように電極のある斜め方向に選択的に析出していることになり、本接続法は「アライメント精度等による位置ずれを析出方向の変化によって吸収する」特異な接続特性を有するといえる。

図 7-10 は、電極幅(5 / 10 $\mu$ m) /ピッチ(10 $\sim$ 50 $\mu$ m) / 対向電極間隔(5 / 10 $\mu$ m) の様々な組合 せパターンを有する TEG において得られた接続状況を、各 TEG ごとに4種類の接続モード(ブリッジ不良(Bridge failure) / 良好な接続(Perfect connection) / 部分的に接続(Imperfect connection) / 未接続(No connection)) に分類して発生割合をリードピッチに対して、チャート図にまとめたものである。ここで、部分的接続(Imperfect connection)は、良好な接続(Perfect connection)と未接続(No connection)が混在している場合を示す。

### **Bridge failure (short circuit)** Perfect connection No connection **Imperfect** connection Mixed Width: 5 µm Width: 10 µm (a) (b) 100% 100% Incidence ratio 80% 80% 60% 60% 40% 40% 20% 20% $20 \mu m$ 25μm 30μm 10µm 15µm 20μm 25μm 50μm 15µm 50µm Lead pitch Lead pitch (d) (c) 100% Incidence ratio oace: 10 μm 80% 80% 60% 60% 40% 40% 20% 20% $20 \mu \text{m}$ 50μm 10µm 15μm 25μm 15µm 20μm 25µm 30µm 50μm Lead pitch Lead pitch

図 7-10 幅 5~10 μm / パッド間隔 5~10 μm の対向電極におけるブリッジ析出状況

図 7-10 において、まず図(a)~(d)のそれぞれのチャートに着目すると、横並びの電極ピッチの減少に伴い、黒塗りの「ブリッジ不良」(隣接電極同士のショート不良)が増加がしていることがわかる。これは横並びの隣接リード同士の接近によりブリッジ析出が増加するためであり、当然の傾向である。一方で、図(a)、(c)、(d)から、電極ピッチの増加に伴い、「未接続」や「部分的接続」等の不完全な析出が増加する傾向があることが分かる。特に(a)では、20μmピッチで 100%良好な接続を示したのに対し、隣接電極との間隔に余裕のある 50μmピッチでは、不完全な析出が 50%以上を占める。このことは、ブリッジ現象による析出膜の成長が単に対向する電極間の配置に依存するだけでなく、横方向に整列する電極との空間的配置によっても影響を受けることを意味する。

次に、同じ電極幅を有する(a)と(c)、(b)と(d)を比較すると、対向する電極間隔(space)の増大( $5\mu$  m $\rightarrow$ 10 $\mu$ m)により「未接続」の割合が増加し、接続性が顕著に低下していることがわかる。析出膜の成長に時間依存性があり、時間の増加に伴い析出距離が増加するとすれば、これは予測される

結果である。また、隣接電極間にブリッジを生じない充分な間隔を有するピッチ(ピッチ≥25µ)に対して、電極間隔が同じ(a)と(b)、(c)と(d)の組合せでそれぞれ比較すると、電極の幅広化がブリッジ析出による接続性を向上させる効果があることがわかる。つまり、対向電極において、電極間隔を小さくし、電極を幅広化することが接続性の向上につながるということができる。

- 2D-TEG-Iによる実験結果から得られた知見をまとめると次のようになる。

- 1) 電極幅(接続幅)に対する電極間隔(接続間隔)の比(=電極間隔/電極幅)を小さくすると、ブリッジ析出による接続性(接続歩留り)が向上する。

- 2)対向する電極間の配置だけでなく、横方向に整列する電極との位置関係により接続性が変化する。電極ピッチが小さすぎる場合は隣接電極とのショート不良を生じ、一方、大きすぎる場合は接続性が低下する傾向がある。

### 7.5.5 時間に伴う Ni-B 膜の析出挙動

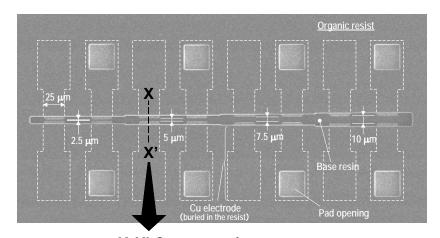

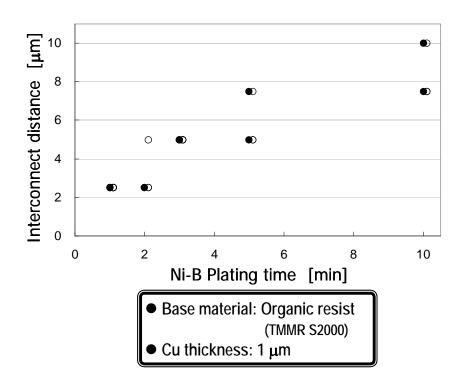

無電解 Ni-B めっきにおけるブリッジ析出現象に関して、時間増加に伴う接続可能距離の変化を有機レジストをベース材とする 2D-TEG-II(図 7-11)を用いて調べた。ここでは、無電解めっき浴への浸漬時間を 1 分~10 分まで変化させて、対向電極に向かって成長した析出膜が、少なくとも薄膜レベルで連続膜を形成した対向電極の中で最大電極間隔を金属顕微鏡及び SEM 観察で確認し、時間に対してプロットした。結果を図 7-12 に示す。

グラフ上の個々の点は、個々のパターンにおける結果に対応し、黒丸(●)は導通測定用のパッドに開口部が無い場合、一方白丸(○)は開口部が有る場合を示す。本プロット図から、多少ばらつきはあるものの、Ni-B 膜のブリッジ析出による接続可能距離が、時間に伴い増加する時間依存性を有することが分かる。また、パッド開口の有無に関しては、今回の結果では有意差は特に見られない。

以上の結果から、ブリッジ析出は突発的に様々な電極間隔で生じるものではなく、その析出距離は、時間に対して単調に増加する傾向があることが実験データにより裏付けられた。

# X-X' Cutaway view 2.5 ~ 10 μm Organic resist (PMER P-LA900M; Tokyo Ohka Kogyo Co., Ltd.) Tokyo Ohka Kogyo Co., Ltd.) Si Base insulator (TMMR S2000; Tokyo Ohka Kogyo Co., Ltd.) (TMMR S2000; Tokyo Ohka Kogyo Co., Ltd.)

$2 \text{ SiO}_2$  (thermally-oxidized film)  $0.2 \, \mu\text{m}$

図 7-11 2D-TEG-II のデザイン概要

図 7-12 時間に伴うブリッジ析出による接続距離の変化

# 7.6 Flip-chip 接続への適用性検証

## 7.6.1 評価用テストチップ (TEG) の設計

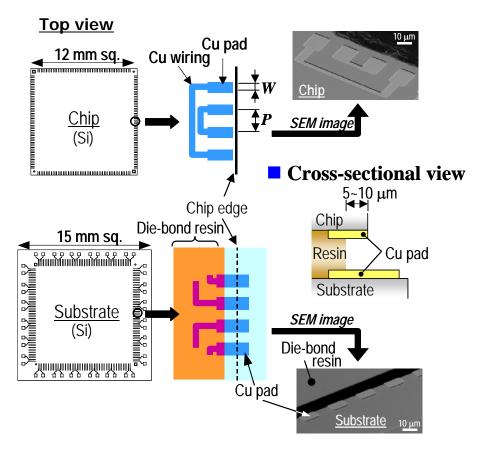

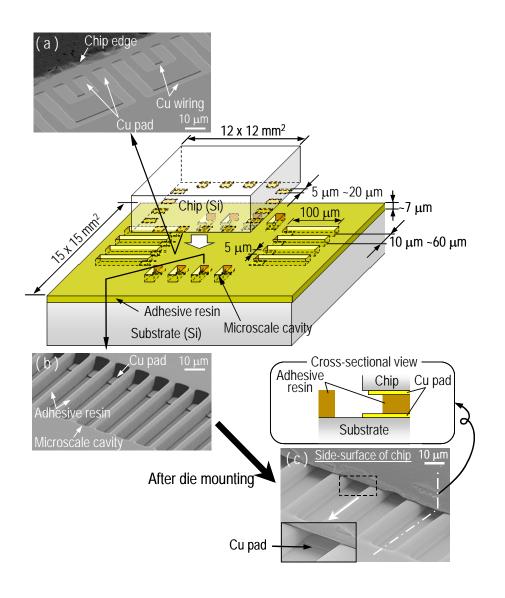

周辺部の対向位置に銅パッド配置した 12 mm 角チップ、15 mm 角基板(Si 製)の組合せによる Flip-chip 接続評価用 TEG(以下 Flip-chip TEG)を作製した。同 TEG の概要を図 7-13 に示す。

### ■ Design parameter of the test chip

| Parameter    |    | Design value [µm] |    |    |    |    |

|--------------|----|-------------------|----|----|----|----|

| $\mathbf{W}$ | 5  | 10                | 20 |    |    |    |

| P            | 10 | 15                | 20 | 30 | 40 | 60 |

- Die-bond material: Organic resist

- (PMER P-LA900M)

- Surface insulator of chip & substrate : SiO2

- Plating time: 3 min.

図 7-13 Flip-chip 接続評価用 TEG の概要

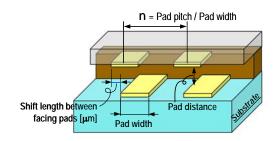

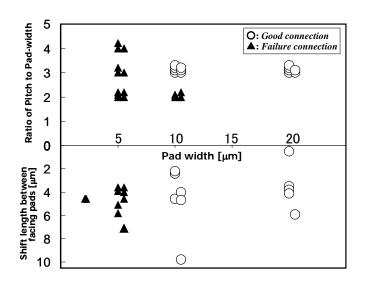

チップ側、基板側それぞれに Cu パターンを形成、Flip-chip 接続時に両者の電極同士が対向するように、周辺部に幅  $5\sim20~\mu m$  /ピッチ  $10\sim60~\mu m$  の Cu パッドを配した。上下パッドの位置関係は、チップと基板を接着するダイボンド樹脂 (レジスト) 塗布後に、断面から見てチップ外形より片側  $5\sim10~\mu m$  だけチップ側の Cu パッドが露出するように設計した。また、その他の配線デザインに関しては、導通試験が可能なようにデイジーチェイン配線及び四端子測定用配線・パッドを設けた。

### 7.6.2 プロセスフローと評価方法

先の図 7-3 に示したように、まず基板側に接着層をスピンコート法により塗布した。接着層の材料としては、現状では本プロセスに適した仕様 (パターニング後に接着性を有する) のものがないため、2D-TEG による平面配置対向電極の評価で用いた電極レジスト用材料 (金めっき用レジスト,東京応化工業製 PMER P-LA900M) を用いた。図 7-13 の断面図に示したように、チップ外形より片側 5~10  $\mu$ m だけチップ側の Cu パッドを露出させ、接着 (ダイボンド) 層にブリッジ接続のベース形状を形成するため、基板側に塗布された接着層 (ダイボンド樹脂) をフォトリソグラフィーにより、チップ外形より片側 5~10  $\mu$ m だけ小さい形状にパターニングした。接着層の厚さ (=対向電極間距離) は、平面配置対向電極で得られた結果を参考にして、3 分のめっき時間で確実な接続が可能なように、ダイマウント後に 5~7  $\mu$ m となるよう、塗布の段階で 7~8 $\mu$ m とした。次にチップを基板に接着 (ダイマウント) させ、両者の対向電極が図 7-13 の断面図に示す配置となるようにした。最後に平面対向電極の接続に用いた DMAB を還元剤とする無電解 Ni-B めっき浴 (60  $^{\circ}$ C) に 3 分間浸漬し、前述の 2D-TEG とほぼ同じプロセス条件 (図 7-5) で、チップと基板間に Ni-B 膜を析出させた。

Ni-B 析出膜による Flip-chip 接続後、接続状況を調べるため、各デザインパターン毎に接続導通チェック、接続部の四端子抵抗測定及び SEM 観察を行なった。

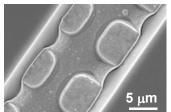

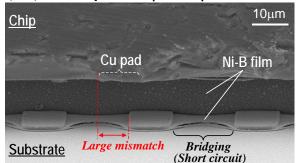

### 7.6.3 Flip-chip 接続後の SEM 観察

図 7-14 に無電解めっきによる Ni-B 析出(3分)後に得られた接続部の代表的な SEM 観察像を示す。図はパッド幅 20 μmーピッチ 60 μm の Flip-chip 接続パターンにおいて、接続部を側面斜め上方向から見た SEM 観察像であり、ダイボンド樹脂層の側面上に、基板上 Cu パッドからチップ上の Cu パッドへ斜めに伸び、やや中央部がくびれた形状の Ni-B 析出による接続膜が形成されていることがわかる。Ni-B 接続膜は、チップマウント時の位置ずれ(いずれも約 4μm)に追従するように斜めに形成されており、Flip-chip 接続においても電極の存在する方向に指向性のある選択的な析出を示すことがわかる。この指向性のある析出現象は本接続法が接続前の位置ずれ(アライメントずれ)に対するトレランスが大きいことを意味し、接続技術の分野では注目すべき特徴である。

図 7-15 は、Flip-chip TEG における接続部の断面(パッド中央部断面近傍)の SEM 観察像である。上下の Cu パッド間にあるダイボンド樹脂の湾曲した側面に沿って Ni-B 析出膜が外側に凸の形状で一様に形成されていることがわかる。析出膜の厚さは約 0.2μm であることが確認され、これは前述の 2D-TEG で観察された Ni-B 析出膜と同じ厚さであることから、チップと基板の Cu パッドを対向電極とする同様な析出現象が行なわれ連続膜が形成されたものと考えてよい。

図 7-14 Flip-chip TEG における無電解 Ni-B めっき後の SEM 観察像 (60µm ピッチ)

図 7-15 Flip-chip TEG における接続部の断面 SEM 観察像

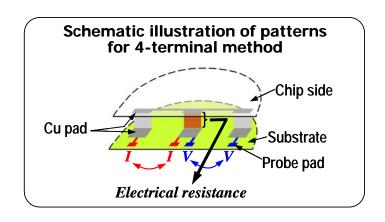

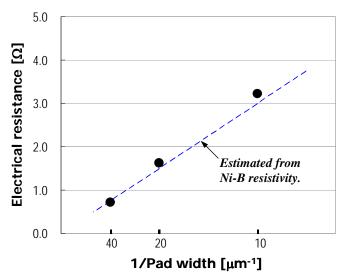

### 7.6.4 ブリッジ接続部の電気抵抗測定

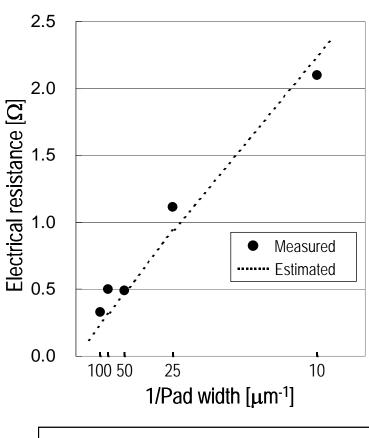

Flip-chip TEG 内に設置された「チップ側/基板側の3つの電極パッドで構成される4端子抵抗パターン」を利用して、個々のブリッジ接続部に関する4端子抵抗測定を行なった。4端子測定は、測定対象となるの1つのNi-B接続部を介してその両側2つのNi-B接続部を経由した電流・電圧測定を行なうことにより行なった。横軸をパッド幅の逆数とした結果を図7-16に示す。Ni-Bの抵抗率(~100 [ $\mu\Omega$  cm])から見積られる抵抗値を図上で直線(破線)で示した。この計算に必要となる寸法に関してはSEM観察結果から、高さ7 $\mu$ m,厚さ0.2 $\mu$ mとして計算した。これより、Flip-chip TEGで得られたブリッジ接続部の抵抗値は、パッド幅の変化に伴い、ほぼNi-Bの抵抗率から予測される値に従って変化していることがわかる。具体的には、幅10 $\mu$ m,20 $\mu$ mのパッド間接続の場合で、それぞれ約3 $\Omega$ ,2 $\Omega$ という値を得た。前述のようにNi-B接続膜はシード層の位置づけであるため、この上にバルクめっき層を形成することにより充分電気抵抗の改善が可能である。

図 7-16 四端子抵抗抵抗測定によるブリッジ接続膜の抵抗測定結果

### 7.6.5 電極間の空間的配置と接続挙動

Flip-chip TEG の接続結果の中から、代表的な「良好な接続例」、「不良接続例」をそれぞれ図7-17に示す。

### **Good connection**

### (a-1) width/pitch : 20 μm/60 μm

### **Failure connection**

(b-1) width/pitch: 5 μm/15 μm

(a-2) width/pitch : 10 μm/30 μm

(b-2) width/pitch : 10 μm/20 μm

図 7-17 無電解 Ni-B めっき析出膜による接続例((a)良好な例, (b)不良例)

図 7-17(a-1)がパッド幅 20 μmーピッチ 60 μm、(a-2)がパッド幅 10 μmーピッチ 30 μm の接続例であり、ともにダイボンド樹脂層の側面上に、やや中央部がくびれた形状の Ni-B 析出による一様な接続膜が形成されていることがわかる。前述のように Ni-B 接続膜は、チップマウント時の位置ずれに追従するように、斜めに成長しており、電極の存在する方向に指向性のある選択的析出現象であることが観察できる。また、Flip-chip TEG において形成されたブリッジ析出膜の形状に着目すると、前述の 2D-TEG におけるブリッジ接続膜と比較して、電極近傍での幅方向の拡がりが少なく、対向電極に対する「成長方向の選択性」が向上していることが分かる。Flip-chip TEG の対向電極が、2D-TEG の対向電極に対して、電極の対向面積を増加させた構造になっていることが関係するものと見られる。

一方、図 7-17 (b-1)、(b-2)は、それぞれ、パッド幅 5 μmーピッチ 15μm、パッド幅 10 μmーピッチ 20μm の TEG で発生した不良接続例である。図(b-1)、(b-2)では、ダイボンド樹脂層の側面全体に一様にNi-B 析出膜が形成されるだけでなく、基板上の隣接パッド間に従来型のブリッジ(ショート)膜が形成され、接続不良を生じていることがわかる。

本接続法では、接続部にパターンマスク等が存在しないため、接続の成否は「析出の選択性」で決まることになる。図 7-17 (b-1)では、上下電極パッド間にピッチの半分に達する大きな位置ずれが見られ、接続不良は、上下パッド間の1対1の対向関係が崩れ、析出方向の選択性が得られなく

なったことに起因すると見られる。また比較的ピッチが大きいにもかかわらず、隣接間にもブリッジが生じている理由は、上記の理由に加え、パッド間距離(ダイボンド厚さ)が大きいことが影響し、上下パッド間に形成される反応生成物による高濃度領域と隣接パッド間に形成される高濃度領域との差が充分得られなくなったことによると推定される。同様に図.3.4-17 (b-2)では、隣接パッド間のピッチの減少により、上下の対向パッド間だけでなく、左右の隣接パッド間においても、ブリッジし易くなり、Ni-B 析出における方向の選択性が低下したため、両方の対向電極間で析出が発生したことにより、ショート不良が生じたといえる。すなわち、いずれの不良例も、めっき前の段階で、析出方向の選択性を得ることが難しい対向電極構造にあったことが接続不良の原因であるということができる。

パッドピッチ、パッド幅が異なるデザインの Flip-chip TEG における SEM 観察像を基に、接続の成否と対向電極の各寸法パラメータとの関係をひとつのグラフにまとめると図 7-18 のようになる。

図 7-18 Flip-chip TEG における各寸法パラメータとブリッジ接続結果 (1)

図 7-18 は、Flip-chip TEG の Cu パッド幅に対して、パッドピッチ (幅に対する比率) 及び対向電極間のずれ量を示す X-Y マップ内に、接続の成否を記号 ( $\circ$ :接続良好, $\triangle$ :接続不良) でプロットしたものである。なお、今回の結果では接続不良 ( $\triangle$ ) は全て隣接電極とのショート不良を示すものである。図から、パッド幅  $5\mu$ m では、隣接パッド間のピッチに関わらず良好な接続は得られず、一

方、パッド幅 10μm 以上では、パッド幅の 3 倍以上のピッチのデザインパッドで良好な接続が得られることがわかる。また、対向電極間の位置ずれに関しては、パッド幅が 5μm 以下では(今回のサンプルのずれ量が全て 4μm 以上あることもあり)良好な接続が得られたものはなく、パッド幅が10μm 以上になると、パッド幅の 1/2 レベルの大きな位置ずれに対しても Flip-chip 接続を達成しており、位置ずれに対する良好な追従性を有していることがわかる。

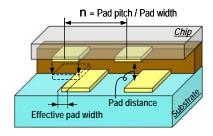

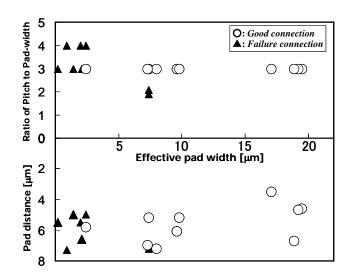

図 7-18 のグラフで「パッド幅」は、設計値に基づく値であり、実際にはパターニング誤差(仕上がり寸法誤差)、チップマウント時の位置ずれ等の影響により、Ni-B 析出前において電極間の対向状態にズレが生じている(図 7-17 (b-1), (b-2))。対向状態を厳密に評価するには、位置ずれ量を盛り込んだ実効的な対向状態を表す指標に変換する必要がある。そこで、向かい合うパッドが実際に対向している幅を SEM 画像から読み取り、これを"実効対向幅"と称して、「実効対向幅ーパッドピッチ」及び「実効対向幅ーパッド間隔」グラフ内に、図 7-18 と同じように接続の良否を記号でプロットすると図 7-19 となる。

図 7-19 Flip-chip TEG における各寸法パラメータとブリッジ接続結果 (2)

本図から、次のことがいえる。

- ① 良好な接続を得るには、実効対向幅が少なくとも 5µmを越える大きさである必要がある。

- ② 実効対向幅が 5μm を越えた場合、ピッチがパッド幅の 3 倍以上の場合には良好な接続性が

得られ、一方、ピッチがパッド幅の 2 倍以下になると、隣接リード間のブリッジ(ショート) 不良が発生する可能性がある。

③①,②の良好な接続条件を満足した場合、時間3分で最大で7μmを越える対向間隔(ダイボンド樹脂厚)に対するFlip-chip接続が可能である。

### 7.7 微細化へ向けたアプローチ

### 7.7.1 微細化のための改良型プロセス

Flip-chip TEG による接続実験の結果から、横並びの隣接リードとのブリッジ不良(ショート)を抑制するためには、電極ピッチを電極幅の3倍以上にする必要があるということが確認された。しかしながら、接続ピッチがバンプサイズの2倍程度のものは、Flip-chip接続のデザインルールとしては極めてポピュラーな部類に属し、狭ピッチ接続への応用を想定した場合、本技術の応用性として大きなマイナス要因となる。そこで、さらなる狭ピッチ化を想定した改良型のプロセスについて検討した。

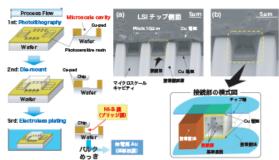

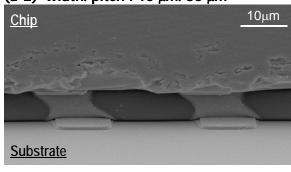

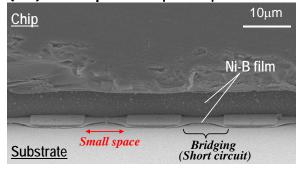

接続にマイナス要因となるこの高濃度領域の形状をベース樹脂の形態で構造的に制御するため、図 7-20 に示す新しいプロセスフローを考案し、接続性を評価した。

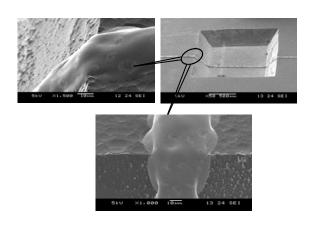

図 7-20 に示したように、最初に、感光性を有する接着樹脂層(レジスト)を Cu 製電極パッドに配した Si 基板表面に塗布し(1)、次に、基板上のパッドが個々に独立して露出するように接着樹脂層にパッドと同程度の幅を有する長方形の孔(以下マイクロキャビティ)をフォトリソグラフィにより形成する(2)。この際、マイクロキャビティの長さはめっき時にめっき液が進入しやすい長さとする。次に、チップと基板双方のパッドが接着後に対向するように、塗布した接着樹脂層を利用してチップを基板上にマウント(ダイマウント)する。この段階において、チップ側と基板側双方の電極パッドが、チップ・基板表面と樹脂により 5 方向を囲まれたマイクロキャビティ内で、対向する状態となる(図7-20(3)断面図)。この後、無電解 Ni-B めっきを行ない、キャビティ内でブリッジ析出による接続膜を形成させ接続を完了する。

この方法では、対向電極面で生成される還元性反応生成物の拡散による高濃度領域は、キャビ ティ内の閉空間に閉じこめられるため、隣接リードとのショート不良を防止できる。

評価に用いた Flip-chip TEG のアウトラインを SEM 観察像と共に図 7-21 に示す。前述の Flip-chip TEG と同じサイズ,同じ構造の Cu パッドを有するチップ,基板に対して、基板側に開口幅 5~20 μm×100 μm, ピッチ 10~60μm のマイクロキャビティをパターニングした。 実際の SEM 観察像を図(b)に示す。 また、チップを接着層によりダイマウントした後のめっき直前の SEM 観察像を図 (c)に示す。 これよりチップ・基板表面と樹脂により 5 方向を囲まれたマイクロキャビティ内で電極が対向している様子がわかる。

図 7-20 マイクロキャビティ構造を利用した狭ピッチ対応型プロセス・フロー

図 7-21 マイクロキャビティを利用した改良型プロセスに供した Flip-chip TEG の構造

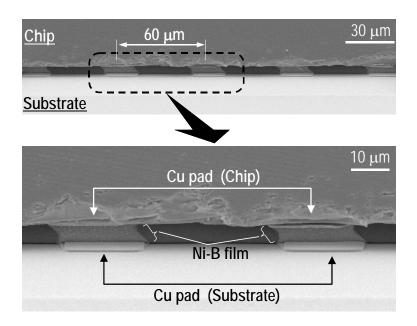

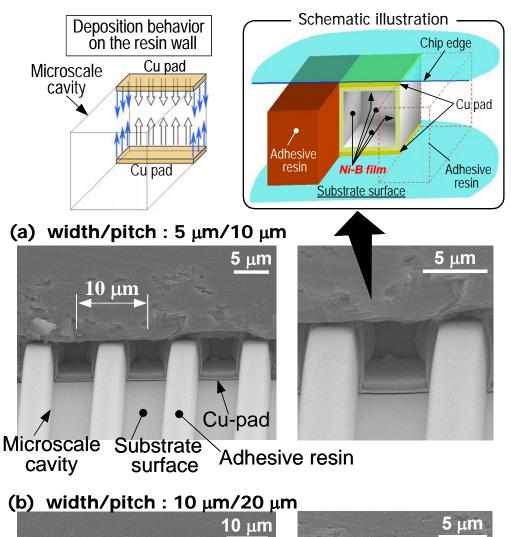

先の Flip-chip TEG と同じ前処理、めっき条件で無電解 Ni-B めっきを 3 分行なった後の SEM 観察像を図 7-22 に示す。(a), (b)はそれぞれ、 $10\mu m$  ピッチ、 $20\mu m$  ピッチの Flip-chip TEG の接続後の接続部を側面斜め上方向から見た SEM 観察像である。模式図に示したように、いずれの場合も対向電極に挟まれたマイクロキャビティ内の 3 つの接着層の樹脂壁面 (左側/奥側(ダイボンド樹脂側面)/右側)上に Ni-B 析出膜が形成されていることがわかる。特に図(b)では、ダイマウント時の加圧により変形した接着層の壁面に沿うような形で Ni-B 析出膜が形成されており、Cu パッドの 3 辺を結ぶ 3 つの樹脂壁上を、析出膜がブリッジ析出反応により成長し連続膜を形成した過程の痕跡をみることができる。また、図(a)では、ショート不良無しで  $10\mu m$  ピッチの Flip-chip 接続を達成していることがわかる。大気中、低温  $(60^{\circ}C)$ 、無荷重で  $10\mu m$  ピッチレベルの超微細接続の成功例はほとんど無く、本接続法の狭ピッチに対するポテンシャルの高さを確認することができた。

図 7-22 10μm ピッチ, 20μm ピッチの Flip-chip TEG においてマイクロキャビティ内に形成された Ni-B 析出膜

同じTEG 内に形成されたいくつかの 4 端子測定パターンによる測定結果を断面 SEM 観察像と ともに図 7-23 に示す。 断面 SEM 観察像から、今回の改良型のプロセスによる Ni-B 接続膜が、マ イクロキャビティを用いない従来のブリッジ接続プロセスの結果と同様に、接着樹脂表面上に厚さ

図 7-23 四端子測定による電気抵抗と断面 SEM 観察像

このことから、キャビティ内という閉空間におけるブリッジ析出においても、析出面の数の違いを除けば、同様な均一膜を形成するといえる。グラフ上に本断面図における各寸法と Ni-B の抵抗率

(~100 [ $\mu\Omega$  cm])から見積もられるキャビティ内の析出膜の抵抗値をグラフ上に点線で示す。なお計算では、断面図に示す寸法から構成される長方形(奥側: $5\mu m \times 7\mu m \times 0.2\mu m$ )の析出膜の抵抗値を用いた。これより、マイクロキャビティ内に形成された接続膜の抵抗は、Ni-B の抵抗率から計算される値とほぼ一致することがわかる。具体的な測定値としては、幅  $10\mu m$ , 25  $\mu m$  のパッド間接続の場合で、それぞれ約  $2\Omega$ ,  $1\Omega$  という値を示した。3 面に析出膜が形成されたことにより、前述の図 7-16 の結果( $10\mu m$  幅→約 3  $\Omega$ ,  $20\mu m$  幅→約 2  $\Omega$ )と比較して低い抵抗値になっており、電気抵抗の面からもメリットがあることを確認した。

ここで重要なことは、本プロセスにおいても、基板上の他の部分には、同じ接着樹脂層が存在し、サンプル全体を浸漬したにもかかわらず、マイクロキャビティ内の対向電極部に挟まれた部分のみに析出が生じていることである。マイクロキャビティを設置したとしても、対向電極間のみに析出膜が成長するという析出の選択性は重要なポイントとなっているといえる。

以上の実験から、無電解 Ni-B めっきのブリッジ析出による対向電極間接続法は、各対向電極を隔離するマイクロキャビティを併用することで、10μmピッチのレベルの接続が可能なことを実証することができた。本手法は、少なくともキャビティ内に対向電極が存在する必要があるため、キャビティサイズの縮小に伴い対向電極間の位置ずれに対する追従性は低下するが、狭ピッチ化による隣接パッド間のショート不良を防ぐことができるため、今後の 10μm 以下のピッチの超微細接続に対して応用性の高い接続プロセスといえる。

### 7.7.2 今後の課題

今回の研究では、対向電極間に接続膜を形成することに重点を置いた。このため、接続後の信頼性に関しては未だ着手しておらず、今後接続信頼性に関する評価ワークを行なう必要がある。 但し、実装における信頼性試験は接続・接合材料で全く異なる結果となるため、これを意味のある信頼性試験とするためには、まず第一に本プロセスに適した接着樹脂(ダイボンド樹脂)を開発する必要がある。今後、感光性を有しながらパターニング後も接着性を有し、その後構造材料としても充分耐えうる樹脂の開発が課題となる。

また、これと並行して、現状では予測の域を出ていない Ni-B の析出メカニズムに関しては、定量的な議論を行なうため、析出時のイオン濃度の測定等を含め、現象を把握するためのさらなる実験データの蓄積が必要である。

### 7.8 まとめ

「常温に近い接続温度」、「機械的変形を伴わない接続」という2つの条件を満足する次世代の 微細接続技術として、無電解Ni-Bめっきの導体間ブリッジ析出現象に着目し、平面配置対向電極 による基礎的な接続評価を行なうとともに、Flip-chip接続分野への適用可能性を検証した。その結 果、以下のことが判明した。

- 1) 無電解Ni-Bめっきによるブリッジ析出膜の形成により、無加圧かつ60℃の低温という条件下で30 μm ピッチレベルの Flip-chip 接続が可能なことを実証した。本接続では、アライメント精度等による位置ずれを析出方向の変化によって吸収する特性を有することも判明した。

- 2) ブリッジ析出によるによる接続性は、電極間隔/電極幅の比の値が小さいほど、また、電極の対向面積が大きいほど向上し、その析出距離は時間に伴い増加する傾向がある。10 分のめっき時間において、25μm 幅-1μm 厚の対向電極で最大 10μm の電極間接続を確認した。

- 3) パターニングで形成したマイクロキャビティ構造とブリッジ析出現象を組合せたプロセスを用いることで、10µm ピッチのレベルの接続が可能なことを実証した。

- 4) 今後、信頼性を考慮した接続技術に発展させるためには、本接続技術に適した接着樹脂の開発、プロセスの最適化及びそれによる歩留りの向上を図ることが最重要課題となる。また、現状では不明な点が多い析出メカニズム解明のため、定量的な実験データの蓄積が必要である。

### Ⅲ. 開発成果のまとめ

MEMS-半導体横方向配線技術の最終目標を達成するために、チップ間接続、高周波配線の直接描画に適用可能な MDW ヘッドの最終試作、ならびにインク原料の最適化を完了し、プロジェクト参画企業である東芝㈱と共同し、貫通ビアの段差乗り越え接続や埋め込み接続、RF-M EMSで必要となる3~60GHz帯域の伝送特性やマイクロインダクター形成を実証する。また、微細バンプ形成技術については、電源電流供給の実証やプロジェクト参画企業である東芝(株)と共同し、MEMS チップ-CMOS チップ集積化モジュールの3次元実装化を実証した。

- 1. マテリアル・ダイレクト・ライティング (MDW) 技術の開発では、前回 2Q/4 期に、描画線幅:  $7\sim1$   $0\mu$ m、アスペクト比で1以上、体積低効率:  $5\times10$ -6  $\Omega$ ・cmの微細配線を、シングルヘッドノズルで、約60cm/minの高速描画に成功、本プロジェクト基本計画の最終目標値を上回る性能を達成した。

- 2. GD 法による円錐金バンプ形成について、実用化に向けて企業と共同で堆積条件の安定化、 He ガス使用量の削減に向けたプロセス改良の検討を進めた。選択析出による無電解 Ni めっき 膜による微細ピッチフリップチップ接続について、反応生成物の拡散現象を仮定した FEM 解析 により、選択析出現象の定性的シミュレーション手法を開発した。

最終目標である10µm以下の線幅描画に成功、実用できるレベルの電気特性、高周波特性、密着強度を得ているが、本格的な実用化・製品化には、次の開発ステージで、IJへッドのマルチノズル化と各種対象インク材料に適した2次元描画のための制御技術の開発、インク材料とIJへッドのマッチングによる高安定化技術などを検討する必要がある。

### (1) 目標の達成度

| 研究項目                                         | 目標                                                                                                                  | 成果                                                                                                                                             | 達成度 |

|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| テーマイ<br>マテリアル・ダイレク<br>ト・ライティング(M<br>DW)技術の関発 | (基本計画目標値)<br>直接線板: 5~19pm<br>成成厚み: 5~10pm<br>描画速度: 1cm/min以上<br>成駅速度: 10pm/min以上                                    | 線幅: 7~10µm<br>配線厚み: 5~16µm (重書き無し)<br>描画速度: 60 cm/m i n<br>最小配線関隔: 30µm (複数平行配線のギャップ<br>関隔) @Si、ガラス、ポリイミド、セラミックス基<br>板上、細面基板上への描画も可能、密若強度増     | 0   |

| デ-マ2<br>段差乗り越え直接援画<br>配線技術の開発                | (基本計画目標値)<br>設差: 100μm以上<br>配差プロセス温度: 400°C以下<br>設差傾斜角度: 80°以上<br>配建表面和さ: 表皮深さの値の<br>1/10 (Ra=0.1 μm以下: 3GHz<br>相当) | 段差:500μm<br>最大領斜角度:84°@ヘッドは基板面に対し垂<br>直固定状態<br>体積抵抗率:3×10 <sup>4</sup> 0・cm @ポストアニー<br>ルなし<br>Rs=60mm以下、コプレーナ型伝送路(50μm線<br>幅)で40GHzまでの伝送特性を確認。 | 0   |

| デーマ3<br>低温複合組み立て実装<br>技術の開発                  | フリップチップ実装接合技術<br>接合形成温度: 150~200°C<br>接合寸法: 10~30µm<br>シェアー強度測定<br>位置合わせ制御条件の最適化                                    | 30µm径円能パンプにより1/80低加重<br>無電解めっき法のブリッジ技統により60℃で低<br>温影成<br>フリップチップ実装練度2µm速成                                                                      | 9   |

### (2) 成果の意義

本研究の成果は MEMS の高密度集積化・複合化に貢献できるだけでなく、医療用デバイスや太陽電池、フラットパネルディスプレイなどの大面積デバイスなど広範囲な分野への応用が期待できる。

### (3) 知的財産等の取得

特許: 3件(国内)、1件(海外·PCT)、

### (4) 成果の普及

口頭発表:10件、論文:3件、受賞1件、プレス発表:2件、プレス掲載:8誌、展示会:4回、技術 移転:1件、サンプル提供:2件

### Ⅳ. 実用化・事業化の見通し

### 成果の実用化可能性と波及効果

本事業の成果は、MEMS デバイス、MEMS/LSI などの高密度集積化への応用が考えられるが、 レーザー援用 IJ 技術については、特にシングルヘッドでも対応可能な医療用カテーテルや医療マイクロカプセルなどに、さらに、太陽電池パネルや FDP などの大面積デバイスの配線・補修技術への応用も期待される。実用化には電気接続の高い信頼性や生産スループットが求められるため、 本研究開発事業期間の後、

- ① ウエハレベルでの大量生産や大面積デバイスへの応用を考慮した IJ ヘッドのマルチ ノズル化

- ② マルチノズル化に対応した2次元描画のための制御ソフトの開発

- ③ 各種対象インク材料拡張と I J ヘッドのマッチングによる高安定化技術

- ④ 省資源・省エネルギー対応の小型GDバンプ形成装置の開発

- ⑤ ブリッジめっき法による3次元積層チップの一括接続技術

を民間企業16社との共同研究などを進めて製品化する予定である。

具体的には、III-(4)成果の普及 に記載された民間企業の要望を分析すると、比較的短時間に 実用化の可能性があり、投資額も少なくてすむシングルヘッド系の応用、出口としてはデバイスのリペア応用と中長期的な開発が必要で投資額も大きく実用化に時間のかかるマルチヘッド系の応用 に大別される。それぞれの開発対象に対して、技術移転やコンソーシアムの設立を産総研イノベーション推進室と連携して検討進めている。